|

СПЕЦІАЛЬНІ

ПАРТНЕРИ

ПРОЕКТУ

Определение наиболее профессиональных ИТ-управленцев, лидеров и экспертов в своих отраслях

Кто внес наибольший вклад в развитие украинского ИТ-рынка.

Награды «Продукт года» еженедельника «Компьютерное обозрение» за наиболее выдающиеся ИТ-товары

|

|

5 сентября 2019 г., 12:10

С августа второе поколение процессоров AMD EPYC стало центром притяжения серверных интересов. Семейство чипов под кодовым названием Rome отличается новой необычной архитектурой: вычислительные кристаллы, содержащие группы ядер, интегрированы в единый корпус с узлом обслуживания коммуникаций — I/O Hub, в обязанности которого входит также работа с оперативной памятью.

До того как объединиться на базе архитектуры Zen 2, AMD пережила размежевание DRAM-каналов в Naples — первом поколении процессоров EPYC, у которых группы процессорных ядер владели собственными контроллерами памяти. Основы такой архитектуры восходят еще к процессорам Opteron, когда AMD ступила на порог дома высокой процессорной моды. Корни NUMA — раздельного и неравноправного доступа к ОЗУ (Non-Uniform Memory Access) — оттуда.

Еще до официального представления AMD EPYC Rome Роберт Хормут (Robert Hormuth), вице-президент Dell EMC, заметил, что любые недостатки архитектуры I/O Hub «будут уменьшены за счет больших размеров L3-кэша и более чем удвоенной пропускной способности Infinity Fabric V2».

Шина межпроцессорной связи Infinity Fabric InterSocket (IFIS) в односокетных платформах не используется — соединение кристаллов мультичиповой конструкции строится на основе Infinity Fabric On-Package (IFOP) . А вот топологическая дистанция между вычислительными ядрами и контроллером памяти никуда не делась, что выводит кэш-память третьего уровня на ведущие позиции в архитектуре EPYC Rome.

Кэш, блоками по 16 МБ, обслуживает процессорный комплекс, состоящий из четырех ядер. Суммарно в одном сокете может быть от 32 МБ до 256 МБ сегрегированной L3-памяти. У различных моделей процессоров количество встроенных комплексов разное, но для понимания достаточно и сказанного.

В нашем распоряжении оказалась платформа ASUS RS500A-E10-RS12-U на материнской плате KRPA-U16 с процессором EPYC 7452. Первым делом нас интересовало, на что способен L3-кэш — как основной компенсатор возможных недостатков архитектуры Zen 2. Результаты исследований с помощью собственного программного обеспечения NUMA CPU and RAM Benchmark (NCRB) изложены в статье «Кэш-память L3 как зеркало производительности процессора AMD EPYC Rome». Коротко подведем итоги тестирования.

Латентность L3-кэш процессора AMD EPYC 7452 в однопоточном режиме

Тестирование, выполнявшееся в однопоточном режиме, показало, что зависимость латентности от размера обрабатываемого блока содержит точку перегиба, возникающую ровно на половине объема L3. Анализ, подтвержденный дальнейшими экспериментами, выявил причину неравномерности — дефицит места в TLB (Translation Lookaside Buffer). Это особый тип сверхоперативной памяти, который используется для дескрипторов страниц при трансляции виртуального адреса в физический.

Проблема исчерпания ресурсов буфера ассоциативной трансляции наблюдалась и ранее, в том числе на процессорах Intel. Один из вариантов ее решения — переход с классической 4 КБ гранулярности ОЗУ на «большие страницы», размер которых в 64-битном режиме составляет 2 МБ. Блоков будет меньше, дескрипторов для управления ими тоже — память TLB будет использоваться более рационально.

Беда в том, что вот так просто все взять и заменить не получается: на пути прогресса стоит консервативность программного обеспечения. Внедрение «больших страниц» в прикладном ПО и применение их в коде ядра операционной системы — две отдельные задачи, требующие различных подходов и разных критериев эффективности. А в прикладных программах гранулярность в 2 МБ возможна только в том случае, если разработчик кода позаботился об этом. Не факт, что сие даст общий положительный эффект, потому что «большие страницы» вообще-то воспринимаются как невыгружаемые. Это означает, что в своп-файл их складывать не получится.

Вернемся к реализации L3 в AMD Rome. Точка перегиба в однопоточном режиме на отметке 8 МБ свидетельствует о возможном падении производительности кэш-памяти, особенно при совместном доступе к ней всех четырех ядер процессорного комплекса. Оптимизм Роберта Хормута может оказаться преждевременным, хотя в любом случае объем L3 в новых процессорах AMD впечатляет, чего не скажешь об изделиях конкурента. Анализ различий в реализациях оставляет открытой общую проблему — куда двигаться процессорной индустрии дальше?

7 марта 2019 г., 17:52

Слухам о скором появлении накопителей знаковой емкости 100 ТБ несколько лет. Похоже, цель близка. На лондонском брифинге Technology Live Эяль Шани (Eyal Shani), директор по маркетингу Western Digital, раскрыл технологические детали будущего продукта.

Прорыву поможет симбиоз черепичного метода записи (SMR) и микроволнового способа ее нанесения (MAMR). Сами по себе технологии не новы, обсуждение их сильных и слабых сторон успело угаснуть. Неожиданным является их дуэт.

А еще новое поколение емких дисков будет оснащено сдвоенным актуатором — коромыслом, несущим блок магнитных головок. Его механизм позиционирует головки в заданном месте над пластинами магнитного диска. От его проворности во многом зависят скоростные характеристики накопителя. По идее, два коромысла улучшат производительность устройства. Так, во всяком случае, думал изобретатель этого механизма Финис Коннер. Ветераны помнят компанию Conner Peripherals и ее HDD. В начале 90-х она довела идею двойного актуатора до производства. Потом ее активы и патенты достались Seagate, вернувшейся к концепции независимого позиционирования двух блоков головок.

Почему технология возродилась? Наполнение дисков гелием дало новый стимул разработкам сверхъёмких магнитных носителей в привычном форм-факторе. Сопротивление гелиевой среды вращению магнитных поверхностей ниже, чем атмосферного воздуха. Следовательно, можно уплотнить пакеты дисков в корпусе, а пролет головок сделать ближе к поверхности.

Пионер «гелиевой» технологии, Western Digital не спешила с черепичной записью, предоставив Seagate разобраться с ее недостатками и протоптать ниши — пока не пришло время MAMR и двойного актуатора.

На первый взгляд, от двух приводов позиционирования нет прямой выгоды: каждый обслуживает свой блок магнитных дисков (4 пластины для нижнего актуатора, еще 4 — для верхнего). Одновременного доступа к магнитным дорожкам не предвидится. Получается, производительность HDD со сдвоенным актуатором точно такая же, как и у двух независимых накопителей половинной емкости. В чем же выигрыш?

Производство гелий-наполненных накопителей — весьма дорогостоящее занятие. Упаковав в гермозону двойной комплект, WD сразу экономит и на корпусировании изделия, и на заполнении его благородным газом.

Собрав воедино букет нестандартных технологий, Western Digital надеется не просто нарастить емкость своих HDD, но и предложить их по приемлемой цене. Потребителем накопителей видятся облачные провайдеры, с их объемными архивными базами, держатели «длиннохвостых» массивов остывающих данных, аналитики «болотных данных». Задачам ретроанализа и машинного обучения нужен обширный фундамент.

В этом году Western Digital нас порадует накопителями в 20 ТБ, а уже в следующем диапазон емкости хранения будет расширен от 40 до 100 ГБ.

5 июля 2018 г., 17:50

Компания AMD сделала то, что давно нужно было сделать, — расшевелила напыщенный и самодовольный, но стагнирующий серверный рынок. На все про все им понадобился один лишь год.

Год назад AMD выпустила семейство процессоров EPYC 7000-й серии, выполненных по нормам 14 нанометрового техпроцесса. В основе разработки — архитектура Zen. Конструктивно процессоры скомпонованы в одном корпусе из четырех восьмиядерных кристаллов Zeppelin. Для установки EPYC используется новое поколение LGA-сокетов под названием SP3.

Кремниевая матрица Zeppelin типовая. При необходимости часть ядер в ней может отключаться и тогда потребители получают 8-ядерные процессоры. «Полный фарш» предполагает 32-ядерные чипы с рабочими частотами в диапазоне от 2,7 ГГц до 3,2 ГГц. Технология SMT увеличивает количество ядер за счет удвоения обслуживаемых потоков. Цены — начиная с $400.

Выводя на рынок семейство EPYC, компания AMD ставила перед собой задачу гибкого конфигурирования серверов под нужды пользователя. Процессоры, по ее мнению, должны соответствовать требованиям, предъявляемым к современным вычислительным платформам. Стоимость владения при этом не должна вызывать испуг. В итоге, функциональность процессоров серии EPYC 7000 подействовала на серверный рынок как цунами:

- До 32 высокопроизводительных ядер Zen в одном процессоре

- Коммутация межпроцессорных связей в рамках одного кристалла или между кристаллами одного корпуса с помощью высокопроизводительной шины Infinity Fabric

- Одно- и двухсокетная конфигурации, причем сокету SP3 гарантирована совместимость с процессорами следующих поколений

- Наличие 128 свободных линий PCIe-шины для обслуживания внешних устройств

- Восемь каналов оперативной памяти DDR4 на процессор

- Поддержка до 2 ТБ ОЗУ на процессор

- Прозрачное аппаратное шифрование трафика памяти без необходимости управления им со стороны приложений

- Аппаратное разграничение доступа к памяти в гипервизоре виртуализации, специально разработанное для защиты виртуальных машин и контейнеров от влияния хоста и друг на друга

- Системная логика, интегрированная в процессор (SoC)

Тот факт, что каждый процессор семейства EPYC способен обслуживать до 2 ТБ оперативной памяти по восьми каналам, отдавая платформе 128 линий PCI Express, означает, что удельная насыщенность операциями ввода-вывода в два с половиной разы выше, чем у его конкурента Intel Xeon SP.

Исходя из этого, AMD назвала свое детище «первым в отрасли бескомпромиссным однопроцессорным решением». До момента появления EPYC надежда построить полнофункциональный высокопроизводительный сервер с одним сокетом была довольно-таки призрачной. Трудно переоценить усилия AMD по преодолению данного заблуждения. Компания сделала огромный вклад в концепцию «простых гениальных конструкций».

Теперь корпоративные клиенты больше не будут тратиться на покупку ненужных двухсокетных платформ из-за капризов разработчика. Искусственные ограничения пропускной способности каналов памяти и шин ввода-вывода ушли в прошлое. Вместо недоиспользуемых серверов лучше подумать про соответствие платформы рабочим нагрузкам, выигрывая при этом в энергопотреблении (а значит и в системе охлаждения), снижая параллельно затраты по приобретению и эксплуатации.

Если для решения поставленных задач требуется только однопроцессорное решение, пусть так и будет: почему лишний сокет должен диктовать требования к пропускной способности памяти и определять архитектуру подсистем хранения и/или сетевого взаимодействия?

Оснащенность EPYC восемью каналами памяти и свободными 128-линиями PCIe-шины означает, что серверы могут быть укомплектованы более емким и производительным дисковым пространством на базе NVMe. Мы можем, во-первых, выделять требуемый объем ОЗУ на единицу внешнего хранения, существенно увеличивая количество таких единиц; во-вторых, отказаться от ретаймеров и редрайверов, которые всегда ухудшают время доступа к периферии, да и денег стоят. Характеристики платформ от Intel вчистую проигрывают здесь: насыщенность одного серверного юнита накопителями у AMD будет существенно выше.

А еще переход к однопроцессорным решениям означает экономию, выраженную четырехзначными числами. Например, лицензирование VMware vSphere основано на количестве используемых процессоров в системе, но есть специальные предложения для однопроцессорных систем, где стоимость лицензии снижается на $7610.

Не исключено, правда, что ситуация со временем может и поменяться. Но тем не менее, мы экономим благодаря отказу от dual-сокет в пользу single-сокет без потери производительности, плюс экономия электроэнергии и снижение затрат на охлаждение.

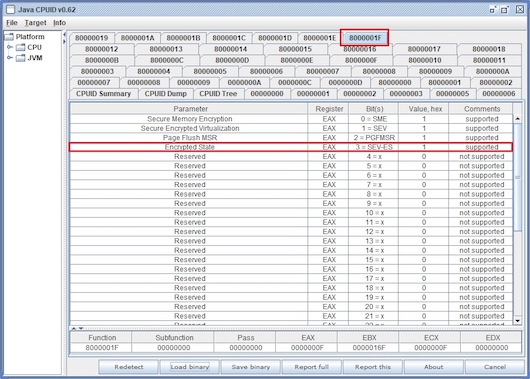

Еще одна область, где EPYC может коренным образом изменить существующий ландшафт серверных парадигм — шифрование памяти. Конечно, аналогичные инициативы есть и у конкурента. Но сравнивая технологию AMD SME/SEV с анклавами защищенных областей Intel SGX, можно отметить, что аппаратное шифрование выполняется прозрачно — без ущерба для производительности на существующем программном обеспечении. Переделка кода не нужна! Другое дело, насколько эти инициативы поддержаны производителями ПО. Хотя, по сути, это всего лишь вопрос времени: обеспечение безопасности давно стоит на повестке дня.

NB. Недавно на презентации Lenovo прямо в зале у меня в руках оказался их ноутбук с процессором AMD Ryzen 5 2500U и графикой Radeon Vega Mobile Gfx. Времени было в обрез, но я успел запустить утилиту Java-CPUID и очень сильно удивился, обнаружив даже в мобильном Ryzen функциональность SEV-ES.

Процессоры от AMD не прячут голову в плечи, когда дело касается соотношения цены к производительности. При бюджете от $400 до $4000 EPYC «вставляет» даже Intel Xeon Skylake. На двухсокетном фронте преимущество AMD не менее 15% для дорогущих чипов в ценовом диапазоне свыше $4000. В нише entry level ($400…$800) ценовой разрыв скачет до неимоверных 56%.

Что действительно поражает в AMD EPYC — это скорость, с какой эти процессоры заняли свою нишу на серверном рынке. Обычно же, игроки там проявляют сдержанность и консерватизм, рыночные тенденции серверостроения весьма инерционны по своей природе. Темпы продвижения процессоров от AMD стали своеобразным индикатором неудовлетворенного спроса. И если ведущие производители, такие как Cisco, Cray, Dell и HP, готовы меняться, их движение в сторону процессоров EPYC — не дешевый ценовой шантаж компании Intel, фактического лидера серверного рынка. Индустрия во весь голос заявляет, что ждет иных решений от законодателей мод.

PS. И в заключение еще одна ремарка. Вполне возможно, что СЕО компании Intel поплатился своей должностью и недавно покинул компанию, допустив саму мысль о возможности разделения рынка серверных процессоров с AMD.

12 июня 2018 г., 15:11

Что ожидает компанию Xiaomi при первичном публичном размещении акций на Гонконгской фондовой бирже, которое вероятнее всего состоится этим летом.

Все предпринимательские начинания безуспешны по-разному и удачливы одинаково – стартаперы в юности читают книги о Стиве Джобсе и дают себе слово следовать «заветам Ильича». Не исключение и Лэй Цзюнь (Lei Jun), основатель Xiaomi.

В 1987 году, будучи студентом в Ухане, провинция Хубей, что самом центре Китая на берегу реки Янцзы, он принял решение построить на родине что-то наподобие Apple. Похоже, Лэй Цзюнь в шаге от воплощения своей мечты – летом Xiaomi планирует выйти на IPO с оценкой от 50 до 75 млрд. долларов. Это будет крупнейшее в мире первичное публичное размещение с момента выхода на биржу Alibaba в 2014 году.

Хотя Xiaomi – один из самых успешных брендов потребительской электроники в Китае, но с момента старта продаж смартфонов в 2010 г., трудно сказать, оказались ли эти устройства монокультурой в экологической нише компании. До сих пор неясно, является ли Xiaomi китайским Apple либо позиционирование компании ближе к бизнес-модели Samsung или Sony? А может это просто ритейл с ограниченными возможностями?

Не секрет, что бренд Xiaomi ни на кого не похож. На протяжении многих лет складывался стереотип особой «американской мечты»: сфокусированной, внимательно реагирующей на мнение акционеров, одним словом – предсказуемой компании. В реальности же Xiaomi больше смахивает на перекачанного культуриста, что вполне соответствует китайским представлениям о правилах ведения бизнеса. Это жестко контролируемый, гиперактивный, в некотором смысле авторитарный механизм с четко продуманной структурой распределения активов. Некоторые эксперты называют такой бизнес «разрушителем Китая». Выход на IPO бренда Xiaomi станет проверкой реальной ценности для инвесторов такой модели ведения бизнеса.

В Китае для Xiaomi важнее всего среда обитания, в которой, как и тысячу лет назад (с поправкой на реалии сего дня), важны знакомства с эстрадными знаменитостями, двусмысленные правила, агрессивная конкуренция, близость к мировому производству электроники и быстро меняющиеся вкусы пользователей. С точки зрения теории эволюции, все это позволяет идеально адаптировать бизнес к рыночным условиям. Ускорение, за которое так ратовал Михаил Горбачев, не на словах, а на деле стало лозунгом компании. Xiaomi сделала за последние семь лет больше, чем многие американские фирмы за период в семь раз больший, – почти три четверти из 18 млрд доллл. объемов продаж в прошлом году приходилось на смартфоны, где им принадлежит 7% мирового рынка.

Помимо смартфонов в портфеле Xiaomi есть и сотни других продуктов – от пылесосов до электрических велосипедов и даже 30% небольшого банка.

Еще одна особенность – вливание средств в успешные торговые предприятия, путем покупки в уставном капитале этих компаний небольших долей. Это привело к 20% падению cash flow в период с 2016 по 2017 гг. и имеет нарастающую тенденцию. Между тем жестокая конкуренция в самой Поднебесной не заставила себя ждать: в 2015 году Xiaomi понесла убытки, а в 2016 году резко снизился объем продаж после потери значительной доли рынка смартфонов в Китае.

Небольшое, но растущее число американских фирм, включая Alphabet и Facebook, исповедуют принцип двухклассовго акционирования. «Такой хоккей нам не нужен!» – говорят в Xiaomi и выводят жесткий управленческий контроль на новый уровень: у владельца компании всегда есть большинство голосов. Как и фирмы «Большой тройки» – Baidu, Alibaba и Tencent – Xiaomi имеют «гибридную» структуру, чтобы обходить правила о наличии иностранных акционеров.

Понятие «иностранного акционера» здесь неразрывно связано с оффшорным бизнесом. Холдинговая компания на Каймановых островах, принадлежащая Xiaomi, имеет контракты с операционными подразделениями в Поднебесной. Так, впрочем, поступают многие представители китайских деловых кругов, например, – Yulong, владелец бренда Coolpad. Эти контракты дают прибыль и возможность управлять бизнесом, но не права собственности, которая остается в руках Лэй Цзюня. Понятно теперь, почему именно он олицетворяет бренд, привлекающий молодежь.

Достоинства Xiaomi являются продолжением его ошибок. «Ручное управление» означает быстрые решения, а близость к поставщикам дает возможность «торговать воздухом» – и компания демонстрирует потрясающие темпы роста. Пока транснациональные корпорации ищут на карте штат Уттар-Прадеш, Xiaomi с 2014 года стремительно развивает там с нуля самое большое производство смартфонов в Индии. До 2017 г. продажи их потребительской электроники утраиваются(!), а в самом 2017 году растут на 68%. Базовая операционная прибыль в текущем году должна, по предварительным оценкам, составить более 1,5 млрд. долл.

Все это оправдывает высокую оценку IPO? В Xiaomi говорят, что они находятся на полпути к иному измерению бизнеса, от с̶о̶х̶и̶ ̶производства к интернету. И понятно почему: за исключением Apple и Samsung, рентабельность производственной отрасли ужасна. Операционная маржа у Xiaomi составляет около 1% (милый треп на тему 5%, адресованный пользователям, не стоит принимать во внимание).

Бизнес, поставивший все на разработку и выпуск аппаратного обеспечения (вспомним, например, трудности Nokia в 2007 г.), годами пожинал мрачные плоды. Услуги – вот новый спасательный круг! У Apple, которая продает приложения, контент и внедряется в платежную среду, доход на базе аппаратной платформы iPhone, iPad и Mac уже 1,3 млрд долл. В прошлом году продажи услуг составили $26 за устройство или в валовом исчислении 33 млрд долл.

У Xiaomi пользовательская база состоит из 190 млн. смартфонов. Они тратят в среднем по 54 минуты в день на свои услуги (приблизительно 20% трафика), что приносит $9 с одного пользователя в год на рекламе и комиссионных от продажи игр, приложений и пр. Если компания сможет сохранить динамику продаж на рынке смартфонов, удвоив доход от услуг с одного пользователя, ее бизнес может стоить 35 млрд долл., надежно подпитывая оценку на IPO.

Кратко о рисках: они есть. Главный из них – падение доли Xiaomi на рынке смартфонов и, как следствие, сокращение числа потребителей услуг. Еще одна проблема – взаимоотношения с зарубежными пользователями. Украина не в счет, а вот продажи услуг на одного пользователя в Индии по-прежнему мизерные. Чего не скажешь о Baidu, Alibaba и Tencent – они как раз-то и расширяют свои экосистемы услуг и могут основательно потеснить Xiaomi с этого рынка. Чтобы остаться на плаву, компании, вероятно, придется реинвестировать в расширение клиентской базы большую часть средств вырученных из IPO, ориентировочно речь идет о 10 млрд долл.

Из сказанного выше следует, что ставка на Xiaomi не может дать ясную перспективу в силу постоянных рысканий стратегического курса. Это, правда, самый минорный сценарий. А еще в спину дышит плеяда новых бизнесов, ожидающих IPO. Здесь и перспективная Didi-Chuxing, которая предлагает интересные транспортные решения, диверсифицированные платежными проектами, и Meituan-Dianping с необычным подходом к поставкам продуктов питания. Вспомним, что у каждого из китайской «Большой тройки» были свои харизматичные идеи, определившие успешное IPO: Alibaba просетапила электронную торговлю, Tencent делает игры, а Baidu действительно что-то ищет.

Сегодня можно констатировать, что Xiaomi, созданная Лэй Цзюнем, – это не китайская копия Apple. Если ему удастся провести свой корабль через биржевые рифы, вместо подражания Джобсу, он сам станет объектом для подражания.

22 марта 2018 г., 13:53

Процессоры AMD получат аппаратную защиту — во внутренней архитектуре CPU появится барьер для вредоносного кода.

Как известно, одной из главных проблем защиты от уязвимостей Spectre и Meltdown является обеспечение безопасности при минимальной потере производительности. Иначе, предпринимаемые в борьбе с вредоносным кодом меры могут оказаться более вредоносными, чем этот самый код. Можно констатировать, что компания AMD подошла к вопросу достаточно основательно, определив тактические и стратегические направления.

Тактика и стратегия

Для краткосрочной перспективы разработана и оптимизирована методика программной минимизации рисков, связанных с работой ранее выпущенных процессоров. Этому посвящен документ Software Techniques Managing Speculation on AMD Processors.

Полное решение проблемы подразумевает аппаратную модернизацию чипов, а именно — функциональные расширения архитектуры процессоров. Набор таких расширений и формализацию их детектирования через инструкцию CPUID описывает документ AMD64 Technology Indirect Branch Control Extension.

Суть предлагаемой защиты — в создании аппаратного барьера на пути вы-полнения программного кода, манипулирующего техниками переходов и ветвлений. Преследуются две цели: держать в руках нити управления вычислительными процессами и блокировать зондирование «запрещенной» памяти спекулятивными операциями. Планируется, что принимаемые меры обеспечат надежный заслон против уязвимостей Spectre и Meltdown.

О текущем положении дел

Исследуя сегодняшнюю способность процессоров AMD противостоять хакерским атакам отметим, что они хотя и готовы к инициативам разработ-чиков, состояние внутренней защиты далеко от желаемого. Проанали-зируем архитектуру AMD Ryzen 5 1600 Six-Core Processor на геймерской платформе MSI X370 XPower Gaming Titanium.

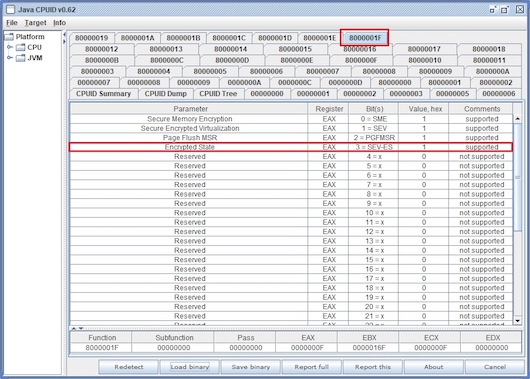

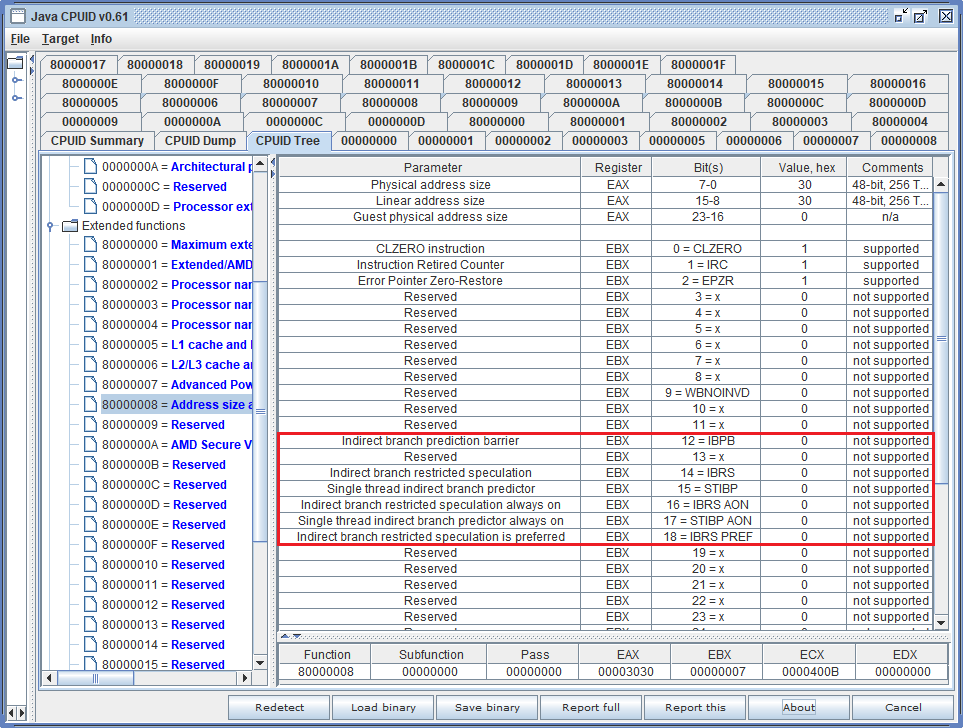

Рис 1. Результат работы утилиты JavaCrossPlatformCPUID v0.61: содержи-мое регистра EBX после выполнения функции 80000008h

Утилита JavaCrossPlatformCPUID, разработанная в IC Book Labs, дает представление о битовых полях и объектах внутренней архитектуры процессора, ответственных за внедрение защиты против зловредного кода.

Как видим, регистр EBX после выполнения функции CPUID 80000008h должен содержать битовые флаги, свидетельствующие о наличии расшире-ний «Indirect Branch Control Extension», заявленных в означенном выше корпоративном документе.

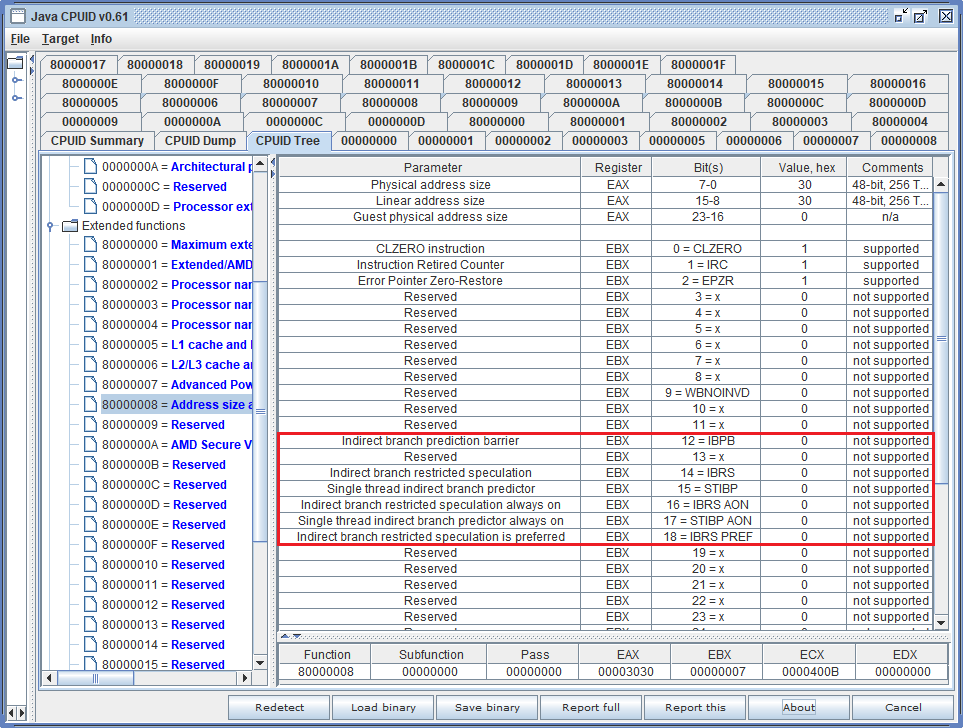

Рис 2. Регистр EBX после выполнения функции CPUID 80000008h содержит битовые флаги, индицирующие наличие функциональных расширений

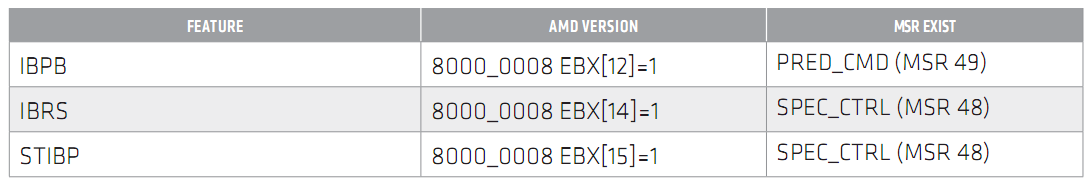

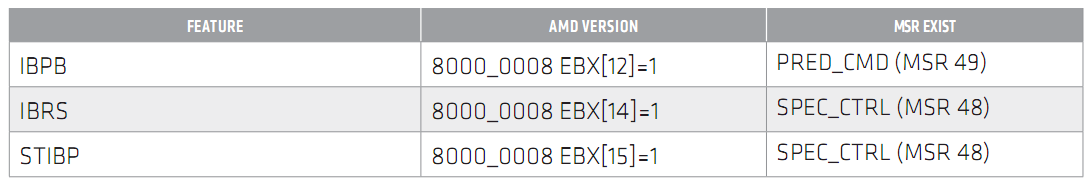

Их функциональность можно разделить на три составляющие, каждая из которых декларируется раздельно:

-

Indirect Branch Prediction Barrier (IBPB)

-

Indirect Branch Restricted Speculation (IBRS)

-

Single Thread Indirect Branch Predictor (STIBP)

Дополнительные поля несут информацию об оптимальных сценариях ис-пользования защиты, обеспечивающих минимизацию ее влияния на произ-водительность процессора.

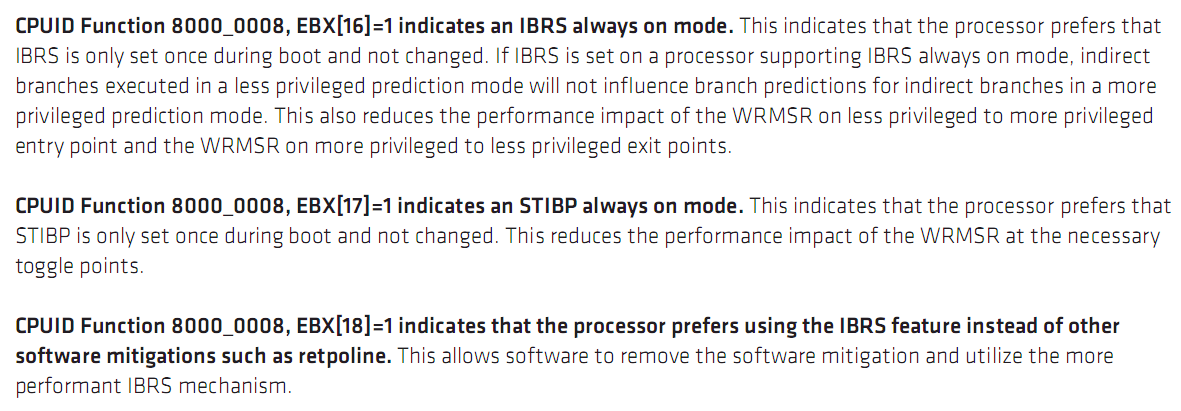

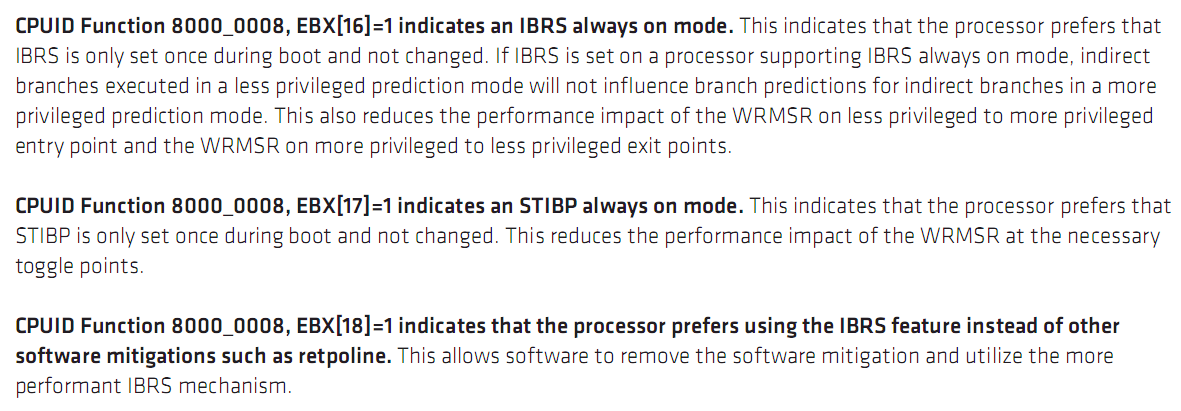

Рис 3. Регистр EBX после выполнения функции CPUID 80000008h содержит битовые флаги, определяющие оптимальные сценарии использования функциональных расширений

Единичное значение флага «IBRS always on mode» означает, что оптимальная производительность достигается в том случае, если режим IBRS будет включен UEFI BIOS при старте платформы и активен постоянно, так как влияние IBRS на производительность минимально. Иначе, предпочтительнее динамическое переключение IBRS в соответствии с привилегиями выполняемого кода. Фактически, это ответ на вопрос, что приводит к меньшим потерям производительности: постоянная активность IBRS или операции переключения режима IBRS.

Флаг «STIBP always on mode» задает аналогичную опцию для режима STIBP.

Флаг «Processor prefers using the IBRS feature» означает, что снижение производительности, обусловленное включением IBRS, меньше, чем при использовании программных техник, таких как retpoline, поэтому задейст-вовать IBRS предпочтительнее не только с точки зрения безопасности, но и производительности.

Таким образом, после выполнения инструкции CPUID, системному програм-мисту доступна информация не только о новых возможностях процессора, но и оптимальных сценариях их использования.

Рассмотрим три составляющие аппаратной защиты.

Indirect Branch Prediction Barrier

Основным объектом атак со стороны вредоносного кода стал Branch Predictor или блок предсказания ветвлений, оптимизирующий выполнение команд косвенных переходов на основании ранее собранной статистики. Способность процессора запоминать предысторию ветвлений, дает возможность атакующей задаче, выполнив фрагмент кода с требуемой по-следовательностью косвенных переходов, влиять на ход спекулятивного выполнения в атакуемой задаче и добывать информацию о последней, пользуясь побочными эффектами, например, — изменением таймингов.

Логичной реакцией разработчиков процессора стала реализация своеобразного барьера, разделяющего два участка выполняемого кода. При этом гарантируется, что статистика выполнения, накопленная до барьера, будет очищена и не повлияет на спекулятивную обработку инструкций JMP, CALL, RET выполняемых после барьера.

В частности, это позволяет осуществить изоляцию гостевых задач вирту-альной машины, а также исключить их влияние на гипервизор виртуализации. Для обозначения точки барьера используется операция записи в один из Model-Specific регистров процессора (PRED_CMD).

Indirect Branch Restricted Speculation

Функциональность IBRS, так же как IBPB, ограничивает возможность злоупотреблений, основанных на спекулятивном выполнении инструкций косвенной передачи управления. IBRS базируется на классических уровнях привилегий Protected Mode и на отношениях «гипервизор-гость» в системах с виртуализацией. Типовой сценарий применения IBRS позволяет исключить влияние процессов уровня пользователя (ring 3) на привилеги-рованные процедуры операционной системы (ring 0), а также влияние гос-тевой задачи на гипервизор виртуализации.

Для включения IBRS используется один из Model-Specific регистров процес-сора (SPEC_CTRL, bit 0). В режиме IBRS, статистика, накопленная при вы-полнении менее привилегированного кода, не будет оказывать влияние на ход спекулятивного выполнения других задач.

Single Thread Indirect Branch Predictor

Опция STIBP, управляемая одним из Model-Specific регистров (SPEC_CTRL, bit 1), также как и две ранее рассмотренные, ограничивает возможности злонамеренного применения предиктора. Функциональность STIBP предназ-начена для решения проблемы, имеющей место в случае, когда несколько логических процессоров (как правило, два) совместно используют общий блок предсказания ветвлений, что дает возможность атакующему потоку воздействовать на атакуемый поток, выполняемый на соседнем логическом процессоре.

Анализируя перспективу

Несмотря на то, что в сегодняшней архитектуре AMD защитный барьер на пути вредоносного кода, эксплуатирующего известные уязвимости CPU, фактически отсутствует, готовность незамедлительно принять меры против несанкционированного доступа к компьютерным ресурсам можно только приветствовать. С тех пор, как процессоры начали использовать обновление микрокода, апгрейд их аппаратной защиты может произойти не только в результате физической замены чипа, но и оказаться приятным сюрпризом для пользователя — после «перешивки» UEFI BIOS, разумеется.

15 марта 2018 г., 12:08

Заметки по поводу знакомства с накопителем Intel Optane 900P, опробованным как в среде Microsoft Windows, так и в операционной системе Linux

Сегодня еще рано делать выводы о перспективах развития технологии 3D XPoint, известной также и под маркетинговым именем Optane. Но первые впечатления от SSD-дисков, ее использующих, полны и восторгов, и раз-очарований. С восторгами все понятно — накопители Intel Optane 900P , уже доступные у нас, феноменально быстрые, с отменной производительно-стью. Без преувеличения. Именно так и есть.

С разочарованиями сложнее. Главное из них — будь операционные системы готовы принять и всемерно поддержать столь быстрые накопители, восторгов стало бы несоизмеримо больше. Мир операционных систем стал бы другим, более динамичным и чуточку персистентным.

Вторая по значимости проблема — функциональность под названием Cont-roller Memory Buffer (CMB), которая отобразит запоминающую матрицу на-копителя в адресное пространство платформы, не обнаружена. А значит, перед нами обычное NVMe-устройство, а не «NVDIMM с интерфейсом PCI Express», на что хотелось втайне надеяться.

Фактически, оба разочарования одной природы и следуют одно из другого. Они похожи, если вспомнить дедушку Крылова, на кафтан — как ни надевай, оголяется часть тела. Ведь чтобы отобразить в оперативной памяти Intel Optane 900P и получать от этого прибавку производительности, требуется изменение самой парадигмы хранения данных. В отсутствие таковой — ракетный двигатель ставим на биплан. А про байтовую адресацию можно просто забыть до лучших времен (здесь уместна отсылка к публикации и обсуждению статьи «Intel Optane 900P: соблазны бьют сомнения» Жуковского и Тищенко).

Конечно, гибкость адресации оптановой памяти, несмотря на блочную природу устройства хранения, сыграла свою роль в упрощении и ускорении алгоритмов, выполняемых встроенным процессором накопителя. Отсюда и выдающаяся производительность. Но хорошо ведь жить еще лучше?

7 сентября 2017 г., 12:53

Не верьте тем, кто говорит о стабильности x86-архитектуры, одновременно надеясь на ее умеренную эволюцию. И с эволюцией по-разному, и о стабильности можно только мечтать: о проекте Itanium ни слова, а на совместимости с x86 первой крест поставила AMD. Я не о доминирующей сегодня системе команд AMD64, она же Intel EM64T. Я о принципах старта персональной платформы, которая в момент появления по эффекту была близка к праздничному фейерверку. Но, как говорится, недолго музыка...

Все это время Intel методично развивал процессорное хозяйство — сначала рост частот, затем — рост количества ядер, каналов памяти. Сокет за сокетом компания пришла к тому, что в самых многоядерных чипах предложила концепцию Cluster-on-Die, которая оказалась не готова к стремительному росту количества процессорных ядер.

На повестке дня новое веяние — 2D-mesh интерконнект для поддержки высокопроизводительных параллельных вычислений. Проблемы с этим у процессоров общего назначения возникли не сегодня, но благодаря крипто-валютчикам с особой остротой встала актуальность и неотвратимость архитектурной трансформации. В майнинге CPU выполняют роль «официанта», неспешно принимающего и раздающего блюда, приготовлением которых заняты многочисленные квалифицированные и высокооплачиваемые «повара» — видеокарты.

Вряд ли такое положение дел устраивает Intel. Обещания сделать доступными 512-битные вычисления не упредили ситуацию, а плетутся в ее хвосте. Но, похоже, Bootable Xeon Phi становится реальностью. На наших глазах разворачивается, как сейчас модно говорить, баттл между концепцией SIMD от Intel и ее соперником от NVIDIA — моделью SIMT. Вся разница в последней литере: Single Instruction Multiple — Data или Thread? Вот в чем вопрос.

Кит все-таки выполз на сушу и по ходу схватки со слоном себя оптимизирует. В его активе огромное число процессорных ядер, каждое из которых пусть и не очень производительно, но кумулятивный эффект вычислительной сети на кристалле дорогого стоит.

Другой вопрос, как это все будет греться при экстремальных нагрузках? У AMD совсем недавно между строк пресс-релизов прозвучал тезис, что можно принести в жертву производительность одного отдельно взятого ядра (речь там шла про ARM), добиваясь его ничтожно малого теплорассеивания, если количество ядер возрастет многократно — в десятки, а то и в сотни раз. Оптимизацию вычислений при таком архитектурном подходе можно делегировать компилятору, как это ранее было сделано в Itanium, хотя на этом все аналогии с ним у ARM и заканчиваются.

Избежать «тепловой смерти» (будем реалистами — отложить апокалипсис x86) можно пожертвовав чем-то не главным. Как это было при переходе к 64-битной архитектуре: тогда пришлось отказаться от операций десятичной коррекции («отряд не заметил потери бойца»). На сей раз люстрация коснется MMX-операций. При наличии 512-битных регистров тянуть за собой воз совместимости с операциями, разрядность которых в 8 раз меньше не имеет смысла. Легкий налет иронии дает отсутствие значимого ПО для More Money eXtraction. Ну, у 1С точно нет оптимизации под MMX, а будет ли под AVX512 — это не моего ума дело.

Следующим в «расстрельном списке» идут операции с дорогими мне портами ввода-вывода. В свое время появление этой архитектурной новации выгодно отличало x86 от мастодонтов типа IBM/360. Но уже на заре Pentium-эры стало понятно, что IN/OUT не поспевают за эволюцией, оставаясь рудиментом и атавизмом. Когда для инициализации системной логики Intel предложил вместо портов технологию конфигурационных регистров в пространстве памяти (memory-mapped), стало понятно, что отказ от них — вопрос времени. Мало кто задумывался, правда, о том, что логичным финалом станет исчезновение портов и операций с ними (привет, совместимость).

Есть еще две группы инструкций, с которыми мы скоро распрощаемся насовсем. Вряд ли они на слуху у широкой публики, да и сказанного вполне достаточно для короткого вывода — балласт в x86 идет за борт полным ходом. «Хьюстон, у нас проблемы!»

22 марта 2017 г., 11:44

Начало поставок твердотельных накопителей на основе технологии Optane сопровождается интересными публикациями, авторы которых неплохо информированы. Если на страницах интернет-изданий публикуется качественная аналитика, места для полемики остается не так уж много. Но существуют и дискуссионные заявления, с которыми можно и нужно поспорить. Одним из таких мессиджей стала способность энергонезависимой памяти Intel Optane (в отличие от классической NAND, оперирующей страницами и блоками от сотен байт до единиц мегабайт) выполнять индивидуальную перезапись байтов. NAND на лопатках? Расходимся? Если и расходимся, то только во мнениях с авторами статьи «Intel’s first Optane SSD: 375GB that you can also use as RAM».

Безусловно, использование Optane в качестве памяти с произвольным доступом — без ограничений, связанных с блоками и страницами, в академичном смысле аббревиатуры RAM (Random Access Memory), — важный шаг на долгом пути сближения характеристик энергонезависимой и оперативной памяти. Ведь классическая NAND-память имеет блоковую архитектуру, и для перезаписи одного байта в блоке его необходимо полностью стереть, а затем повторно записать с измененным значением байта. На время выполнения операции Block Erase исходное содержимое блока требуется скопировать в область временного хранения в оперативной памяти.

Еще одна тонкость в том, что блоки разделены на страницы. Если размер блока (типовое значение — единицы мегабайт) определяет гранулярность операции стирания, то размер страницы (типовое значение — десятки килобайт) определяет гранулярность операции записи, при условии, что блок, к которому относится записываемая страница, был предварительно стерт.

С маркетинговой точки зрения довольно велик соблазн сопоставить суммарное время записи одного байта в NAND (включая операции с блоками и страницами) и время физической записи только одного байта для Intel Optane. Выигрыш новой памяти при таком сценарии исчисляется разницей в несколько порядков. А устранение процессов стирания и повторной перезаписи блока, позитивно влияет на такой важный параметр, как endurance.

В реальности же традиционный стек протоколов, обеспечивающий функционирование mass storage устройств под управлением ОС, ориентирован на блоковые операции, в которых адресуемым квантом является сектор, размером 512-4096 байт. При этом способность физического носителя к индивидуальной адресации байтов останется практически не востребованной, за исключением некоторых служебных операций встроенного программного обеспечения накопителя. Это означает, что серьезных дивидендов от индивидуальной адресации байтов следует ожидать после появления модулей NVDIMM на основе технологии Intel Optane. На очереди обновление инфраструктуры, позволяющие декларировать такую функциональность, передавая информацию от UEFI платформы к ОС посредством ACPI-таблицы NFIT.

О чтении

Одним из факторов повышения производительности операции чтения для рассматриваемых SSD устройств, является внутренняя аппаратная поддержка, подразумевающая динамическое формирование тракта передачи данных, минуя встроенный микроконтроллер накопителя и минимизируя участие его firmware. Любопытно, что данный подход антагонистичен по отношению к созданию дополнительных посредников (типа Storage Processor) в диалоге дисковой подсистемы и центрального процессора.

27 февраля 2017 г., 13:27

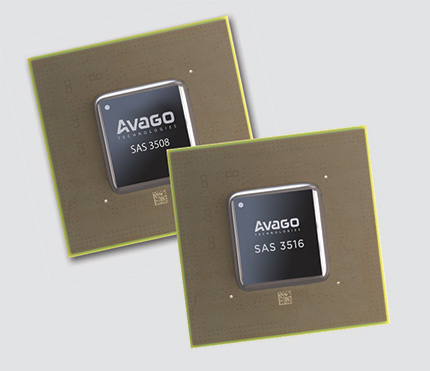

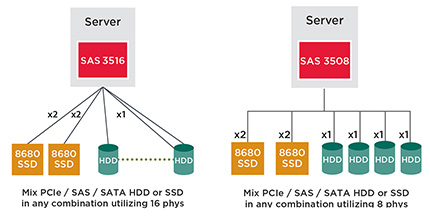

«У вас в сервере будет столько накопителей, сколько вы сможете подключить, а у нас — сколько мы захотим». Так или приблизительно так можно рассказать о новом семействе RAID-контроллеров SAS3508/3516 от Avago Technology. И с некоторой натяжкой это будет правда.

Компания Avago под брендом Broadcom закрыла прореху в технологической нише управления внешними устройствами. Во-первых, новый контроллер одинаково хорошо позаботится о всех типах серверных накопителей — SAS, SATA или NVMe. Tri-Mode этому имя.

Во-вторых, снимается вопрос с построением аппаратных RAID-массивов на твердотельных дисках, подключаемых к шине PCI Express. Впервые, кстати.

В-третьих, вся логика организации RAID и управления вводом/выводом поместилась в одном чипе. Это теперь модно и называется ROC (RAID-on-Chip). Адаптеры с контроллерами SAS3508 или SAS3516 (их уже выпускает Dell и Lenovo) занимают совсем немного места, что важно для компоновки 1U-серверов. Теоретически, монтаж этих контроллеров возможен и на PCB системной платы, но до этого вряд ли дойдет.

В-четвертых, контроллеры от Broadcom хиторомудрым способом (без ГМО и пестицидов!) позволяют существенно улучшить эластичность дискового хранилища.

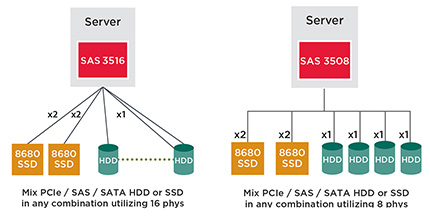

Чем ограничено количество используемых NVMe?

Особенность архитектуры PCI Express — ограниченное количестве линков (дифференциальных пар). Вот почему слотов расширения, обеспечивающих доступ к производительной PCIe-шине, формируемой CPU, всегда недостаточно. Особенно остро это ощущается на 1U-платформах. По сути, имея в распоряжении один слот PCI Express x16, как хочешь, так и строй дисковый NVMe-пул, где каждое устройство требует x4-линк.

NVMe ROC от Broadcom дает возможность задействовать один PCIe x8 слот (что вызывает ряд вопросов к производительности SAS3516) для обслуживания нужного количества PCIe(NVMe)-устройств. Контроллер SAS3516 Tri-Mode RAID-on-Chip (кодовое название Ventura) «потянет» 16 накопителей, SAS3508 (по внутренней кодификации Harpoon) — восемь. Системный интегратор лишен хлопот с ретаймерами и редрайверами. Обо всем позаботился Broadcom.

Для чего нужна сериализация/десериализация?

SerDes в названии чипов означает эффективное использование ими трафика шины большей разрядности, к которой они подключены, для трансляции его (трафика) на несколько вторичных шин меньшей разрядности, где «сидят» NVMe.

Вполне понятно, что, например, механически x16 линк PCI Express никак не получится разнести на четыре PCIe x4 линка. Для сопряжения шин различной ширины это следует поручить логике. Обработка информации контроллерами SAS3508/ SAS3516 и дает право говорить о сериализации/десериализации.

Кратко о перспективах

Наращивая количество накопителей, не стоит забывать про их объемы. Особенно, с учетом построения многослойных хранилищ. Если кэширование и тиринг «горячих данных» всегда прерогатива скорострельных NVMe-дисков, для файлового mass storage желательно бы иметь небыстрые, но надежные и емкие магнитные диски с интерфейсом SAS (хуже — SATA).

Перспектива свести воедино информационные потоки и эффективно ими управлять — явно по плечу SAS3508/3516. Его трехмодовость делает лишними дополнительные SAS-адаптеры. Плюс экономия на системной плате: выбираем без бортового RAID-контроллера. Возможность совместить устройства различных типов позволит реализовать компромиссы стоимость/производительность, комбинируя емкие и медленные диски для редко используемых данных, а маленькие и быстрые — для мета-данных или интенсивного трафика.

Отдавая должное NVMe RAID-контроллеру Broadcom с поддержкой SAS/SATA (по слухам, аналогичные решения вот-вот появятся у Adaptec/Microsemi), нельзя пройти мимо откровенно слабых мест в его архитектуре:

-

Наивно рассуждать о построении полноценных NVMe RAID-массивов на SAS3508: максимальная производительность предполагает всего два x4-подключения. Это значит — «зеркало» или strip, и уже без SAS-слоя.

-

Можно строить отказоустойчивый NVMe-массив на PCIe x2 линках с дополнительным хранилищем на SAS/SATA. Тогда на презентационной блок-схеме нужно отобразить еще один сервер с доступом к этим же накопителям, а сами они нужны в двухпортовом исполнении.

-

Адаптер с SAS3516 на борту, казалось бы, лишен недостатков младшего контроллера. Но если верить документации Broadcom, его узким местом становится первичная PCI Express шина с x8 линком. Ему бы x16, чтобы не иметь проблем с производительностью.

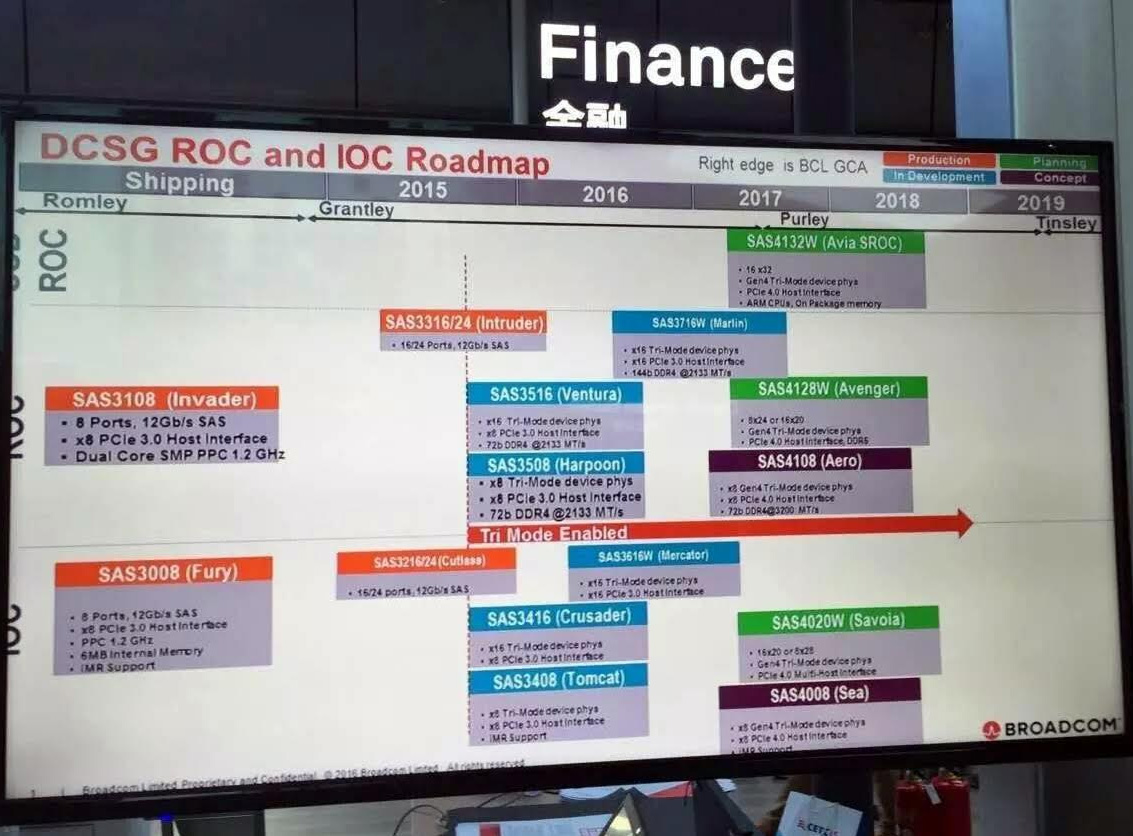

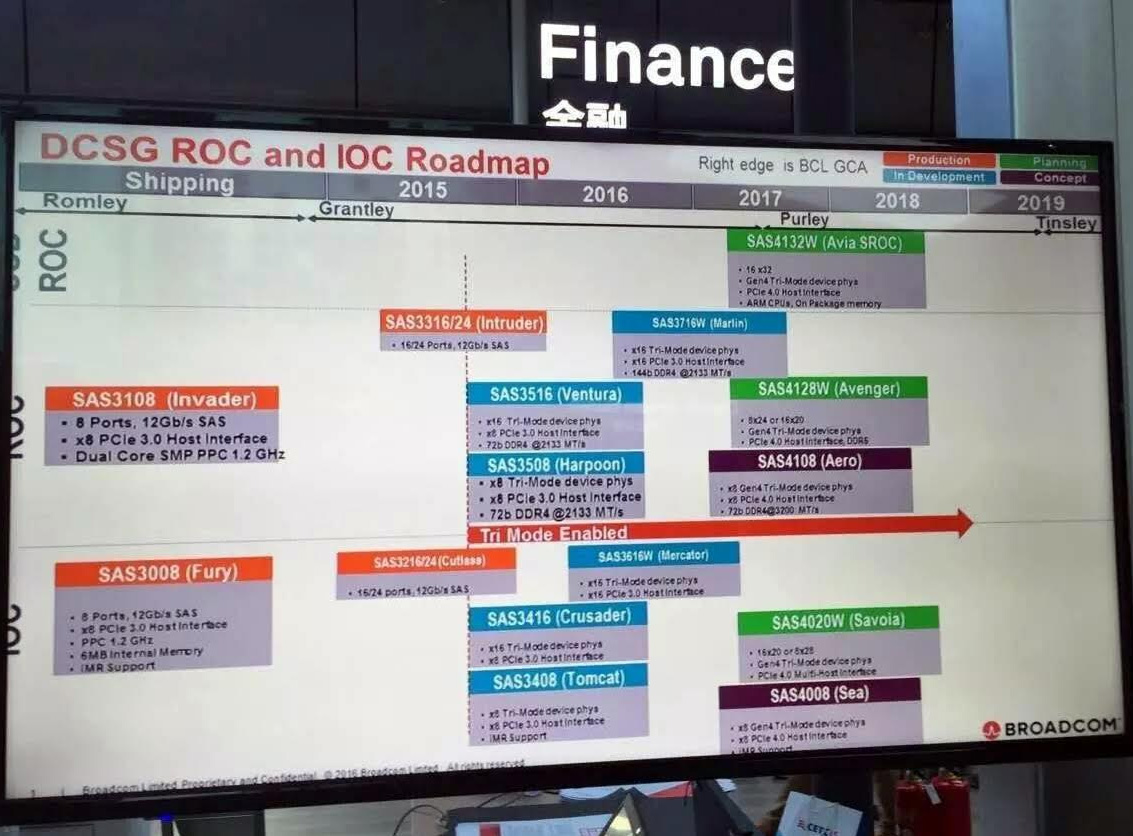

Решать проблемы Broadcom собирается уже в этом году. Компания активно работает над новым поколением контроллеров. Это будут чипы с поддержкой спецификации PCI Express 4.0, рассчитанные на обслуживание x32 линков. Вот тогда и заживем, как люди!

22 февраля 2017 г., 12:33

Для тех, кто следит за новинками IT-индустрии, это не стало неожиданностью, ведь появление энергонезависимой памяти Intel Optane стирает грань между постоянными и оперативными запоминающими устройствами (частично, конечно). Попробуем разобраться, насколько уместна аналогия между S.M.A.R.T. жестких дисков и аналогичной функциональностью модулей энергонезависимой памяти. Поможет нам в этом пример реализации конфигурационного интерфейса NVDIMM, адресованный компанией Intel разработчикам драйверов и UEFI-приложений.

Почему классический S.M.A.R.T. не годится для Optane-памяти?

Вспомним, что получить атрибуты S.M.A.R.T. магнитного или твердотельного накопителя можно обычной ATA-командой. Очевидно, что энергонезависимый модуль не доступен по этому методу, значит, для считывания конфигурации требуются иные подходы.

Альтернативный метод идентификации NVDIMM-модулей предоставляется ACPI-интерфейсом, в частности — NFIT-таблицей. Для получения параметров мониторинга в рабочем сеансе ОС (например, температур), компания Microsoft предложила DSM-метод, описывающий алгоритм взаимодействия с ресурсами платформы. Его необходимо выполнить в системе команд AML (ACPI Machine Language) для получения запрошенных значений.

В число таких операций, обеспечивающих поддержку NVDIMM в рамках интерфейса ACPI, входит доступ к атрибутам S.M.A.R.T и пороговым значениям параметров, чтение и установка меток, а также ряд специфических для каждой конкретной платформы функций.

Очевидно, физическим интерфейсом для доступа к конфигурационной информации NVDIMM-модулей, в типовом случае будет шина System Management Bus, используемая для системного мониторинга и чтения содержимого SPD традиционных DIMM-модулей. В общем случае физическая реализация SMBus-контроллера при таком подходе должна быть инкапсулирована в UEFI BIOS. Это означает, что информационно-диагностическая утилита, запускаемая в сеансе операционной системы или UEFI, может получить всю требуемую S.M.A.R.T.-информацию, не имея сведений о конкретной архитектуре системной логики. Хотя необходимость интерпретации AML-кода и не позволяет сказать, что задача для программистов от этого слишком уж упростилась.

Почему в S.M.A.R.T. нет унификации?

Обсуждая особенности реализации, не упустить бы из виду, что главное назначение S.M.A.R.T. состоит в оценке состояния устройства, анализе и протоколировании операционных режимов, управлении резервированием пространства носителя в обеспечение его живучести, а равно прогнозировании его отказов. Вместе с тем, ознакомившись со списком параметров, доступных для модулей энергонезависимой памяти, констатируем, что унификации подходов для NVDIMM и SSD здесь не произошло.

Даже такое казалось бы общее место, как температуры накопительной матрицы и контроллера, обслуживаются по разному и доступны для раздельного чтения. Само понятие S.M.A.R.T.-атрибутов и набор величин, значение которых можно программно идентифицировать, существенно иные. В который раз приходится признать очевидное: NVDIMM — это не HDD.

|

|

|