Як на порядок прискорити роботу AI-моделі

4 сентябрь, 2025 - 16:35Тимур ЯгофаровСтартап d-Matrix, що розробляє цифрові обчислювальні чіпи з вбудованою пам'яттю, представив нову технологію 3D-пам'яті (3DIMC), яка обіцяє в 10 разів прискорити роботу моделей штучного інтелекту та скоротити енергоспоживання на 90% порівняно з поточним галузевим стандартом HBM4.

Компанія була заснована у 2019 році генеральним директором Сідом Шетом (Sid Sheth) і технічним директором Судіпом Бходжа (Sudeep Bhoja), обома керівниками компанії Inphi, що розробляє високошвидкісні міжмережеві з'єднання, яку у 2020 році за 10 млрд дол. придбала компанія Marvell. Її метою є розробка технології обчислювальних чіпів в оперативній пам'яті, яка забезпечує більший обсяг пам'яті для AI-висновків, ніж традиційна пропускна здатність DRAM, при цьому за значно менших витрат, ніж пам'ять з високою пропускною здатністю (HBM).

Сід Шет опублікував у LinkedIn: «Ми віримо, що майбутнє AI-висновків залежить від переосмислення не тільки обчислень, але й самої пам'яті. Ми прокладаємо шлях для нової парадигми обчислень у пам'яті (3DIMC), яка дозволяє нашій платформі DIMC продовжувати масштабуватися і пробивати межу пам'яті без втрати місткості та пропускної здатності пам'яті. Шляхом тривимірного укладання пам'яті та її більш тісної інтеграції з обчисленнями ми значно зменшуємо затримку, покращуємо пропускну здатність і відкриваємо нові можливості для підвищення ефективності».

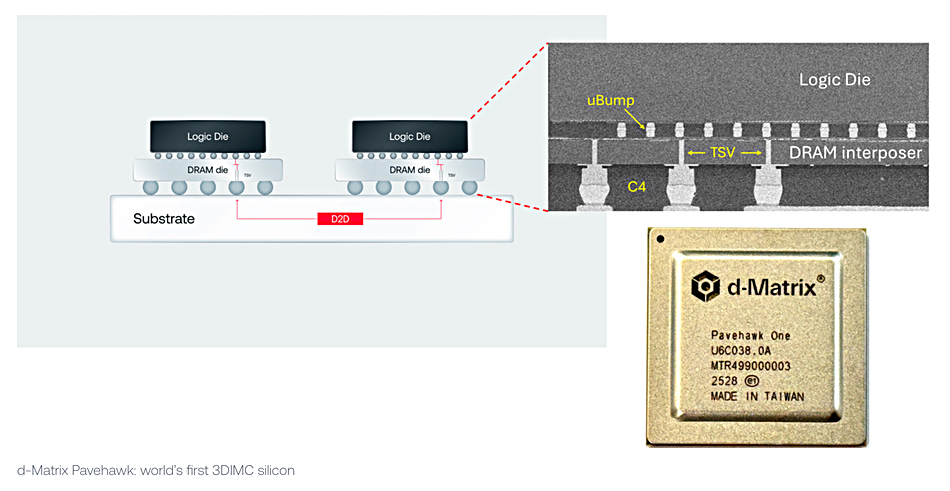

Технологія d-Matrix використовує пам'ять LPDDR5 з цифровим апаратним забезпеченням для обчислень у пам'яті (DIMC), підключеним до пам'яті через інтерпозер. Механізм DIMC використовує модифіковані комірки SRAM, доповнені транзисторами для виконання множення, щоб виконувати обчислення в самому масиві пам'яті. Він побудований за архітектурою чиплет і оптимізований для множення матриць і векторів, операції, що використовується в моделях на основі трансформаторів. Обчислювальні ядра Apollo містять вісім блоків DIMC, які паралельно виконують множення матриць 64×64, підтримуючи різні числові формати (наприклад, INT8, INT4 і блокову точку, що плаває).

Бходжа написав у блозі: «Ми впроваджуємо в наш план найсучаснішу реалізацію 3D-накопичувального цифрового обчислення в пам'яті, 3DIMC. Наш перший кремній з підтримкою 3DIMC, d-Matrix Pavehawk, який розроблявся понад 2 роки, зараз працює в наших лабораторіях. Ми очікуємо, що 3DIMC збільшить пропускну здатність і місткість пам'яті для робочих навантажень штучного інтелекту на порядки та забезпечить, що з появою нових моделей і додатків постачальники послуг і підприємства зможуть ефективно і недорого запускати їх у великих масштабах».

«Наша архітектура нового покоління, Raptor, буде включати 3DIMC у свій дизайн, використовуючи досвід, який ми та наші клієнти отримали під час тестування Pavehawk. Завдяки вертикальному укладанню пам'яті та тісній інтеграції з обчислювальними чипсетами, Raptor обіцяє прорвати межу пам'яті та відкрити абсолютно нові рівні продуктивності та TCO».

«Ми прагнемо досягти в 10 разів кращої пропускної здатності пам'яті та в 10 разів кращої енергоефективності при виконанні завдань штучного інтелекту з використанням 3DIMC замість HBM4. Це не поступові досягнення, а стрибкоподібні поліпшення, які переосмислюють можливості масштабного штучного інтелекту», - зазначив він.

Примітно, d-Matrix пройшла два раунди фінансування. У 2022 році в рамках раунду A було зібрано 44 млн дол., а у 2023 році в рамках раунду B — 110 млн дол., що в сумі становить 154 млн дол. Компанія має партнерські відносини з постачальником серверних компонентів GigaIO.