| +66 голосов |

|

За десятилетия бурного развития процессоростроения мы уже так свыклись с регулярным уменьшением технологических норм выпуска микросхем, которое нашло свое отражение в Законе Мура, что кажется, будто иных путей наращивания производительности и быть не может.

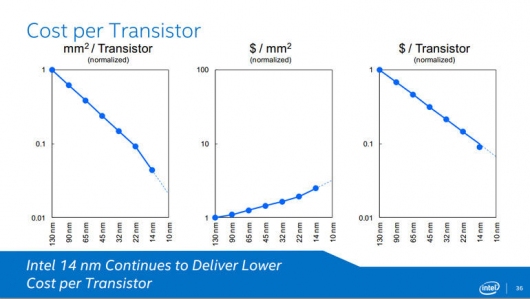

Дискуссия о дальнейших путях развития микроэлектроники прошла в рамках ежегодной конференции ISSCC, которая прошла в Сан-Франциско. Интересно, что кроме технологических факторов, здесь много говорили об эффективности вложения средств. О традиционном подходе масштабирования путем сокращения допуска рассказывали представители тех компаний, что оперируют объемами выпуска чипов, исчисляемых в миллионах, В первую очередь, это Intel и Samsung. Так Марк Бохр (Mark Bohr) проиллюстрировал этот подход очень наглядной инфографикой, показывающей постоянное снижение удельной стоимости транзистора и удельной площади пластины с каждым следующим переходом на новый техпроцесс.

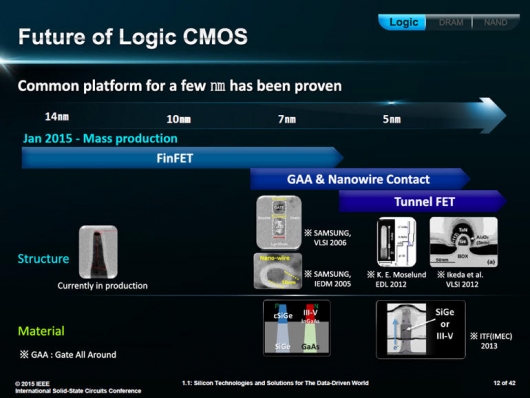

На его графиках обозначен пока только 14-нанометровый, но есть все основания полагать, что аналогичный шаг по снижению удельной стоимости будет сделан и при внедрении 10 нм. По мнению представителя Intel, предельным пока является порог в 7 нм, после которого индустрии нужно будет предпринимать какие-то радикальные меры: внедрять новые материалы для канала либо новые структуры типа туннельных полевых транзисторов.

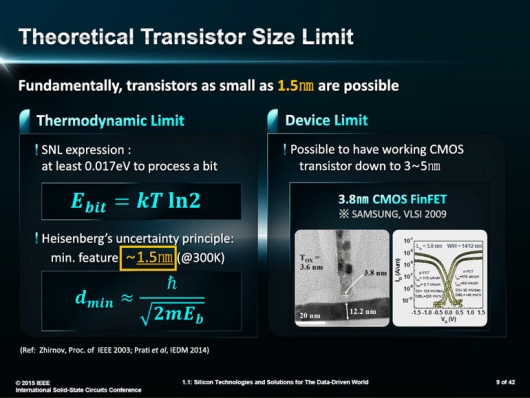

Немного дальше пределы традиционного масштабирования отодвинул глава Samsung Semiconductor Кинам Ким (Kinam Kim), по его мнению, CMOS-транзисторы могут сокращать свои размеры до 3-5 нм, хотя уже при 7 нм потребуются некие хитрости.

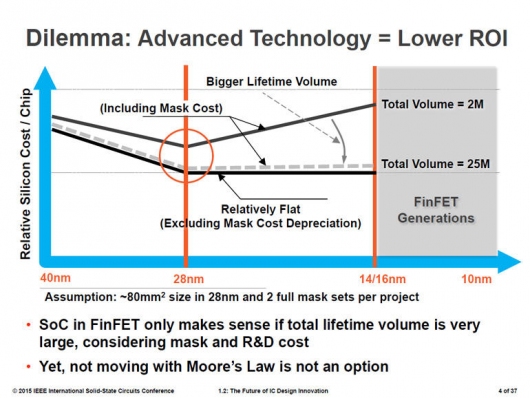

А вот в других выступлениях на ISSCC перспективы сокращения технологической нормы не представлялись уж настолько радужными, и вот почему. Дело в том, что связанные с этим расходы на исследования и создание масок требуют настолько больших расходов, что за порог в 28 нм они могут быть окуплены лишь при объеме выпуска чипов не менее 25 млн шт. А такое тиражирование достигается считанными игроками уровня Apple и Samsung. Поэтому-то и приковано внимание индустрии к альтернативным путям наращивания производительности.

Например, Xilinx видит наиболее эффективным выполнять более плотную упаковку вентилей в архитектуре 2,5D или 3D, сокращая по возможности соединения, что позволяет расширить полосу пропускания и снизить энергопотребление. При этом предлагается заменять одно массивное ядро несколькими небольшими, но с более высоким выходом годных, а объединять их будет высокоскоростная шина.

Примечательно, что представитель Qualcomm Джефри Яп (Geoffrey Yeap) вообще поставил под сомнение насущной необходимости в масштабировании, а куда более важным является предоставление покупателю каких-то дополнительных функциональных бонусов. С этим точно не поспоришь, вопрос лишь в том, что это за бонусы и как их реализовать. Как бы то ни было, а Qualcomm это удается, а ведь представленные ею недавно новые чипы Snapdragon 400 и 600 выпускаются TSMC с использованием процесса 28 нм. Как видим, фокус на цене и обеспечение весьма сжатых сроках вывода решения на рынок позволяют Qualcomm добиваться успеха.

Еще один подход к созданию платформ представила Marvell. Ее модульный дизайн под названием MoChi предусматривает использование вычислителей, соединяемых с периферией с помощью фирменной скоростной шины AXI. По замыслу Marvell, таким образом можно формировать виртуальные системы на чипе (Virtual SoC) с доступной ценой, причем они могут гибко настраиваться на различные сегменты, включая смартфоны, ноутбуки, серверы и активное сетевое оборудование. Некий аналог LEGO, но на уровне микропроцессора.

Как видим, индустрия стоит перед проблемой – как именно строить мост через показавшуюся на горизонте пропасть и строить ли его вообще. Идти в лоб и тратить невероятные средства на поиск новых материалов и дальнейшую миниатюризацию либо попытаться обойтись имеющимися возможностями наиболее эффективным образом.

Стратегія охолодження ЦОД для епохи AI

| +66 голосов |

|