Si-IF стирает границы между чипами

За последние несколько десятилетий кремниевые схемы уменьшились в 1000 раз, но сами физические размеры чипов на платах — лишь в четыре раза. Устранить эту диспропорцию может технология кремниевых межсоединений, Silicon Interconnect Fabric (Si-IF), совместная разработка Калифорнийского университета (UCLA) и Университета штата Иллинойс в Урбана-Шампань.

С помощью Si-IF инженеры рассчитывают на одной кремниевой заготовке построить компьютер с 40 графическими процессорами. Как сообщил Сэмюэль Мур (Samuel Moore) из IEEE Spectrum, в симуляциях этот многопроцессорный монстр обеспечивает ускорение вычислений почти в 19 раз, а также уменьшает потребление энергии и задержку сигнала более чем в 140 раз. Фактически он работает не как совокупность 40 графических процессоров, а как единый GPU, увеличенный в 40 раз.

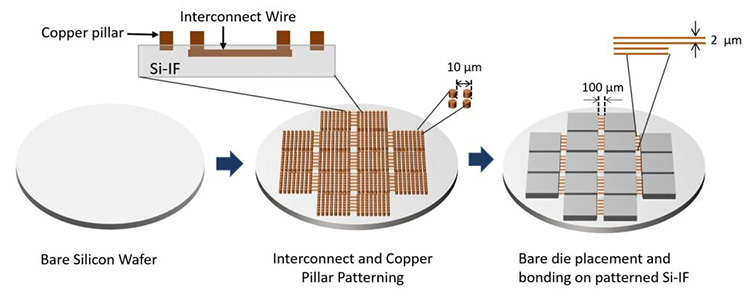

Пластина Si-IF состоит из одного или нескольких слоев медных межсоединений шириной 2 микрометра, расположенных на расстоянии всего 4 микрометра друг от друга. Это сопоставимо с плотностью межсоединений на чипе. В местах, где должны подключаться графические процессоры, на кремниевую пластину нанесены короткие медные столбики, расположенные на расстоянии около 5 микрометров друг от друга. Графический процессор точно совмещают с ними, после чего запрессовывают и нагревают. Этот хорошо отлаженный процесс, называемый термокомпрессионным соединением, заставляет медные столбики сплавляться с медными же межсоединениями графического процессора.

Преимущества процессоров уровня заготовки (waferscale) были очевидны ещё в 80-е годы прошлого столетия, когда было предпринято несколько коммерческих попыток их создания. Все они потерпели неудачу из-за недостаточного выхода годной продукции, делавшего невозможным массовое производство. Доля брака возрастает с увеличением размеров процессора, и для масштабов целой заготовки она была преобладающей.

Теперь, спустя 30 лет, с учётом достигнутого за этот срок прогресса в технологиях полупроводникового производства, пришло время пересмотреть вопрос о рентабельности waferscale-процессоров.

Участники совместного проекта подготовили статью «Architecting Waferscale Processors — A GPU Case Study». О своих последних достижениях они расскажут на международном симпозиуме IEEE по высокопроизводительным компьютерным архитектурам, который пройдёт в Вашингтоне (округ Колумбия) 16–20 февраля.