Рекордно малый 3D-транзистор имеет ширину всего 2,5 нм

Всего несколько лет назад стандартная ширина транзистора в коммерческих чипах была около 20 нм. Теперь она составляет 10 нм, причём индустрия быстро переходит на уровень 7 нм — такие процессоры уже работают в iPhone XR, XS и XS Max. IBM даже начала экспериментировать с 5-нанометровыми чипами.

Между тем, даже этот будущий размер смогли уполовинить исследователи из MIT и Колорадского университета. На конференции IEEE International Electron Devices Meeting, состоявшейся на прошлой неделе, они представили модифицированный метод термического атомно-слоевого травления (thermal ALE). Эта техника позволяет последовательно удалять с поверхности полупроводника слои толщиной всего 0,02 нм, обеспечивая немыслимую до сих пор точность формирования электронных компонентов чипа.

«Вы как будто снимаете кожицу с луковицы, слой за слоем, — говорит Вэньцзе Лу (Wenjie Lu), первый автор статьи. — В каждом цикле мы можем убрать всего два процента нанометра материала. Это дает нам очень высокую точность и тщательный контроль за процессом».

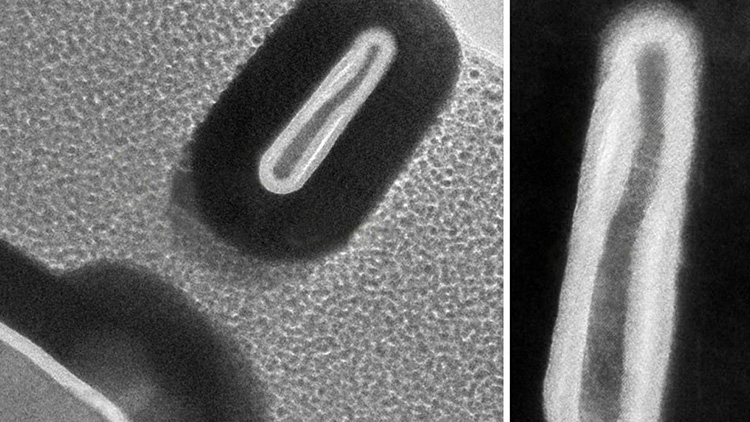

Изготовленные новым способом 3D-транзисторы FinFET имели размеры менее 5 нанометров, а наименьшие — всего 2,5 нм. Эти устройства в испытаниях работали (до 60%) лучше коммерческих FinFET и имели более высокий контраст включённого и выключенного состояний, что делает их более энергоэффективными.