Многоэтажная конструкция улучшит работу чипа в 1000 раз

Десятилетиями компьютерные схемы напоминали пригородный посёлок с одноэтажными зданиями — чипами для обработки и хранения данных. Оборотной стороной простоты такой архитектуры были большая длина «улиц» по которым распространялись сигналы, и регулярно возникающие заторы при передаче данных, большие затраты энергии и времени.

В Rebooting Computing, специальном выпуске журнала IEEE Computer, инженеры из Стэнфорда вместе с учёными из трёх других университетов рассказали о Nano-Engineered Computing Systems Technology (N3XT) — новом, «многоэтажном», подходе к конструированию микропроцессоров и чипов памяти.

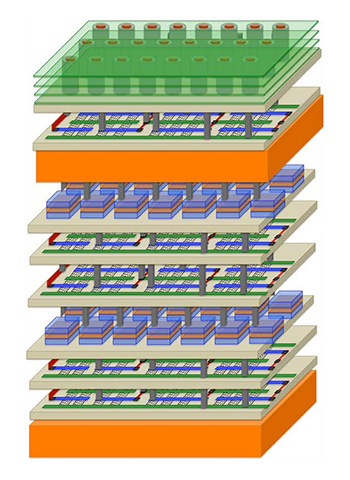

Интегрируя функциональные электронные компоненты подобно этажам в небоскребе, N3XT позволяет перемещать больше данных за более короткое время и тратить на это меньше энергии, чем низкопрофильные электронные архитектуры.

Миграция индустрии с планарной на высотную модель потребует гигантских инвестиций, но, в итоге, обернётся и огромным выигрышем. «Сочетая более высокую скорость со сниженным энергопотреблением, N3XT превосходит традиционные подходы в 1000 раз», — утверждает доцент Стэнфорда, Субгаши Митра (Subhasish Mitra).

Создавать многоэтажную схему из кремния трудноосуществимо, так как нанесение каждого очередного слоя требует нагрева чипа почти до 1000°, а это крайне трудно осуществить не повредив уже имеющиеся слои. Поэтому, в сегодняшних кремниевых 3D-технологиях два слоя создаются по отдельности, а уже затем их совмещают и соединяют несколькими тысячами проводников.

Команда N3XT вместо кремния применила новые наноматериалы на базе углеродных нанотрубок (CNT), что позволило создавать слои процессора и памяти непосредственно один на другом, объединяя их миллионами коротких и эффективных связей в электронное суперустройство. Проблема охлаждения такой конструкции решается внедрением теплоотводящих прослоек.

В этом месяце, на International Electron Devices Meeting, Митра продемонстрировал действующий прототип многоэтажного чипа. Это устройство состояло из двух слоёв памяти RRAM, заключённых между двумя слоями CNT.