Дослідники відкрили спосіб "вирощування" транзисторів субнанометрового розміру

Дослідницька група під керівництвом директора Центру квантових тіл Ван-дер-Ваальса Інституту фундаментальних наук (IBS) Джо Мун Хо (JO Moon-Ho) реалізувала новий метод епітаксіального вирощування металевих матеріалів 1D з шириною менше ніж 1 нанометр (нм). Група застосувала цей процес для розробки нової структури для двовимірних напівпровідникових логічних схем. Зокрема, вони використовували одновимірні метали як електрод затвора ультрамініатюрного транзистора.

Дослідження було опубліковано в журналі Nature Nanotechnology ("Integrated 1D epitaxial epitaxial mirror twin boundaries for ultra-scaled 2D MoS2 field-effect transistors").

Інтегровані пристрої на основі двовимірних (2D) напівпровідників, які демонструють чудові властивості навіть за граничної товщини матеріалу аж до атомного масштабу, є одним з основних напрямків фундаментальних і прикладних досліджень у всьому світі. Однак реалізація таких ультрамініатюрних транзисторних пристроїв, здатних керувати рухом електронів у межах кількох нанометрів, не кажучи вже про розробку процесу виробництва цих інтегральних схем, стикається зі значними технічними труднощами.

Ступінь інтеграції в напівпровідникових приладах визначається шириною та ефективністю управління електродом затвора, який контролює потік електронів у транзисторі. У традиційних процесах виготовлення напівпровідників зменшення довжини затвора нижче кількох нанометрів неможливе через обмеження роздільної здатності літографії. Щоб розв'язати цю технічну проблему, дослідницька група використовувала той факт, що дзеркальна подвійна межа (MTB) дисульфіду молібдену (MoS2), двовимірного напівпровідника, є одновимірним металом завширшки всього 0,4 нм. Вони використовували його як електрод затвора, щоб подолати обмеження процесу літографії.

У цьому дослідженні металева фаза 1D MTB була отримана шляхом управління кристалічною структурою наявного 2D-напівпровідника на атомному рівні, перетворюючи його в 1D MTB. Це значний прорив не тільки для напівпровідникових технологій нового покоління, а й для фундаментального матеріалознавства, оскільки демонструє можливість синтезу нових матеріальних фаз на великих площах шляхом штучного управління кристалічними структурами.

Згідно з Міжнародною дорожньою картою пристроїв і систем (IRDS), розробленою IEEE, до 2037 року технологія напівпровідникових вузлів досягне приблизно 0,5 нм, а довжина затвора транзистора становитиме 12 нм. Дослідницька група продемонструвала, що ширина каналу, модульована електричним полем, прикладеним до затвора 1D MTB, може становити всього 3,9 нм, що значно перевершує футуристичний прогноз.

Транзистор на основі 1D MTB, розроблений дослідницькою групою, також має переваги в продуктивності схеми. Такі технології, як FinFET або Gate-All-Around, що застосовуються для мініатюризації кремнієвих напівпровідникових приладів, страждають від паразитної ємності через складну структуру пристроїв, що призводить до нестабільності у високоінтегрованих схемах. Навпаки, транзистор на основі 1D MTB може мінімізувати паразитну ємність завдяки своїй простій структурі та надзвичайно малій ширині затвора.

Директор Джо Мун Хо прокоментував: "Металева фаза 1D, отримана шляхом епітаксіального зростання, - це новий матеріальний процес, який може бути застосований в ультрамініатюрних напівпровідникових процесах. Очікується, що в майбутньому він стане ключовою технологією для розроблення різних електронних пристроїв із низьким енергоспоживанням і високою продуктивністю".

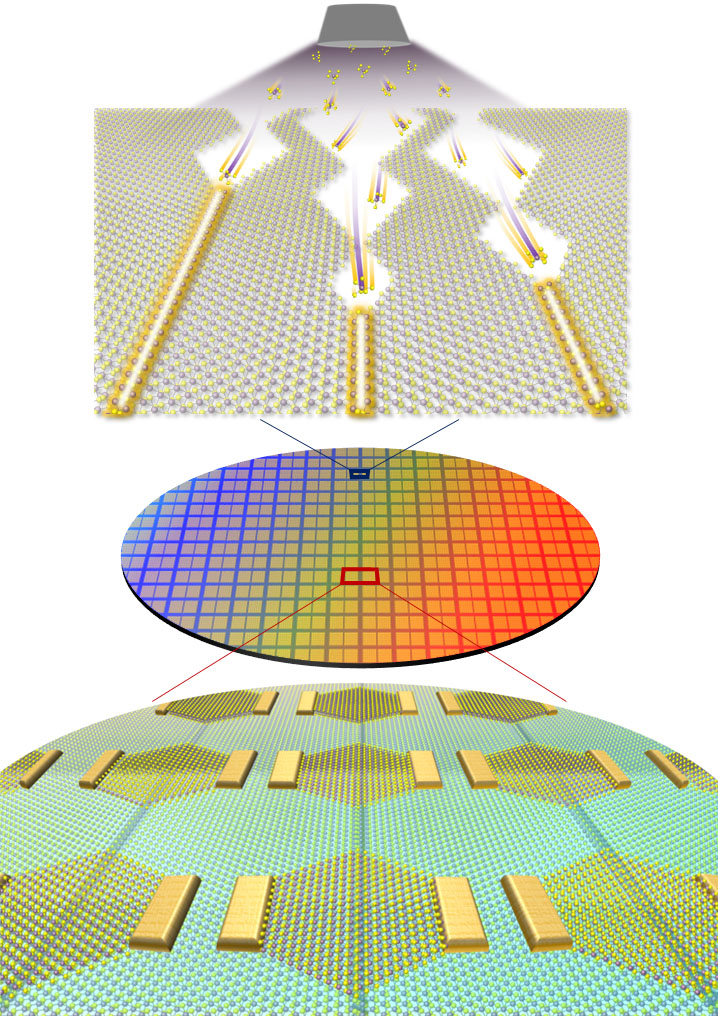

Вирощування металевого дзеркального двійникового кордону 1D і 2D інтегральна схема на його основі. На цьому малюнку показано синтез металевих 1D дзеркальних двійників за допомогою епітаксіального зростання за методом Ван-дер-Ваальса (угорі) і двомірна напівпровідникова інтегральна схема великої площі, побудована на основі цих кордонів (внизу). Контролюючи кристалічну структуру дисульфіду молібдену на атомному рівні за допомогою епітаксіального зростання за методом Ван-дер-Ваальса, можна вільно синтезувати металеві 1D дзеркальні подвійні кордони в бажаних місцях у великих масштабах. Ці межі були використані в якості електродів затвора для реалізації ультрамініатюрних 2D-напівпровідникових транзисторів з довжиною каналу на атомному рівні.

Ультрамініатюрні транзистори та інтегральні схеми з використанням 1D дзеркальних подвійних граничних затворів. На цьому малюнку показано зображення інтегральної схеми на основі 1D-дзеркальних подвійних граничних затворів (зліва), схему ультрамініатюрних транзисторних та інверторних пристроїв, що складають схему (у центрі), і оцінку продуктивності цих пристроїв (праворуч). Розроблений дослідницькою групою процес 1D mirror twin boundary не обмежився мініатюризацією окремих пристроїв, а був успішно використаний для створення високоінтегрованих електронних схем великої площі.