Compute Express Link 2.0

7 ноябрь, 2021 - 16:01Леонід БарашПо мере того как улучшения скорости в соответствии с законом Мура подходят к концу, разрабатываются новые методы, позволяющие обойти узкие места, возникающие из традиционной компьютерной архитектуры фон Неймана. «Фон Нейман» описывает систему с центральным процессором общего назначения, памятью, внешним хранилищем и механизмами ввода-вывода. Потребности в обработке данных постоянно растут, но простого добавления транзисторов в микросхему уже недостаточно для повышения скорости и емкости CPU, памяти и хранилища.

Как показывают две недавние разработки, возникает новая иерархия памяти. В частном порядке Micron отказался от 3D XPoint, а SK hynix раскрыла новые категории и продукты памяти в иерархии скорости доступа. В обоих случаях новая архитектура Compute Exchange Link (CXL) рассматривается как звено, которое связывает общую память и устройства обработки, такие как процессоры, графические процессоры и ускорители для конкретных приложений.

Будущее, связанное с CXL после фон Неймана, изобретается прямо на наших глазах, и оно будет более сложным, чем сегодняшние серверы, поскольку разработчики систем стремятся обойти ограничения нарушения закона Мура.

CXL — это открытый индустриальный стандарт для высокоскоростных соединений с низкой латентностью между центральным процессором (CPU) и устройствами и между CPU и памятью. CXL построен на физическом и электрическом интерфейсе PCI Express (PCIe) с протоколами в трех ключевых областях: I/O, память и согласованность кэша. Он предназначен для решения растущих вычислительных рабочих нагрузок путем поддержки гетерогенных систем обработки и памяти с приложениями в области ИИ, машинного обучения, аналитики, облачной инфраструктуры, облачности сети и периферии, систем связи и высокопроизводительных вычислений. Это достигается за счет включения семантики когерентности и памяти поверх семантики ввода-вывода на основе PCI Express (PCIe) 5.0 для оптимизации производительности в развивающихся моделях использования. Это становится все более важным, поскольку обработка данных в этих новых приложениях требует разнообразного сочетания скалярных, векторных, матричных и пространственных архитектур, развернутых в CPU, GPU, FPGA, интеллектуальных сетевых интерфейсах и других ускорителях.

CXL 1.0 дебютировал в марте 2019 года, поддерживая динамическое мультиплексирование между богатым набором протоколов, который включает семантику ввода-вывода (CXL.io на основе PCIe), кэширования (CXL.cache) и памяти (CXL.memory). CXL поддерживает единое согласованное пространство памяти между CPU и любой памятью подключенного устройства CXL. Это позволяет и CPU, и устройству совместно использовать ресурсы и работать в одной и той же области памяти для повышения производительности, уменьшения перемещения данных и уменьшения сложности программного стека, что приводит к трем основным видам использования, как показано на рисунке 1. Более того, поскольку CPU в первую очередь является отвечающий за управление согласованностью, он может снизить стоимость и сложность устройства, а также снизить накладные расходы, традиционно связанные с согласованностью каналов ввода-вывода. Стандарт CXL 1.1, представленный в июле 2019 года, включает детали тестирования на соответствие.

Рис. 1.Типичные случаи использования, разрешенные CXL 1.0 и CXL 1.1

Основываясь на отраслевом успехе и принятии CXL, о чем свидетельствуют более 130 компаний-членов с активным участием, примерно через год после CXL 1.1 разработчики объявили о доступности CXL 2.0, что позволяет применять дополнительные модели использования при сохранении полной обратной совместимости с CXL. 1.1 и CXL 1.0.

CXL 2.0 расширяет возможности CXL 1.1, представляя три основных области: коммутатор CXL, поддержку постоянной памяти и безопасность.

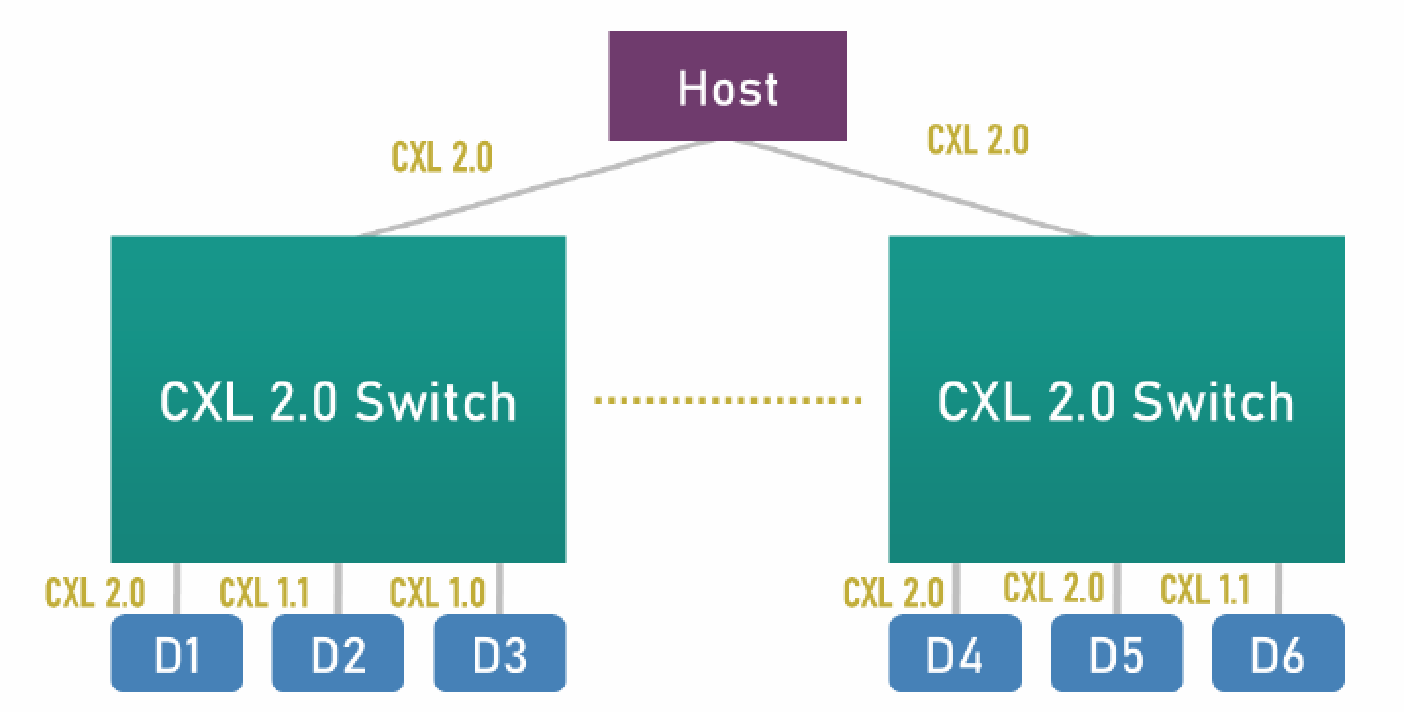

Одной из новых функций CXL 2.0 является поддержка одноуровневого переключения для включения разветвления на несколько устройств, как показано на рисунке 2. Это позволит многим устройствам на платформе перейти на CXL, сохраняя при этом обратную совместимость и низкую задержку CXL.

Рис. 2. Коммутатор CXL 2.0 поддерживает разветвление на несколько устройств при сохранении обратной совместимости

Одним из важных аспектов набора особенностей CXL 2.0 является поддержка объединения нескольких логических устройств (MLD), а также одного логического устройства с помощью коммутатора CXL, подключенного к нескольким хостам (корневым портам). Эта функция позволяет серверам объединять ресурсы, такие как ускорители и/или память, которые могут быть назначены разным серверам в зависимости от рабочей нагрузки. Предположим, серверу нужны две FPGA и GPU, он может запросить эти ресурсы у диспетчера ресурсов в стойке и получить их, если они доступны, и отказаться от них, когда его работа будет выполнена.

Точно так же память может гибко выделяться и освобождаться для разных серверов (то есть узлов или хостов) в зависимости от потребности. Это позволяет разработчикам системы не перегружать каждый сервер в стойке, обеспечивая при этом наилучшую производительность. CXL 2.0 допускает объединение в пул с помощью коммутаторов, подключенных к множественному логическому устройству типа 3 (MLD), как показано на рисунке 3 ниже. Каждый цвет в узле (H) представляет домен или сервер, который определяет иерархию.

Коммутатор CXL 2.0 может обрабатывать несколько доменов (до 16 таких иерархий могут достигать одного MLD). Устройство MLD типа 3 может поддерживать до 16 доменов на каждом из своих портов CXL. Устройство MLD типа 3 также может разделить свои ресурсы CXL и подключиться напрямую к нескольким хостам, каждый с выделенным каналом CXL, как показано на рис. 3. Это помогает с производительностью, идентичной прямому подключению, поскольку задержка коммутатора исключено, что важно для доступа к памяти.

Рис. 3. Объединение устройств CXL в пул с коммутатором CXL 2.0 или без него

CXL 2.0 достигает этих целей, определяя усовершенствования протокола для объединения в пулы, сохраняя при этом качество обслуживания и требования к надежной изоляции для различных доменов. Он также определяет управляемые потоки горячей замены для добавления/удаления ресурсов. Что наиболее важно, CXL 2.0 определяет стандартизированный диспетчер фабрики, чтобы гарантировать, что пользователи будут иметь одинаковый опыт при объединении, независимо от типа устройства, хоста, коммутатора или моделей использования, которые у них есть.

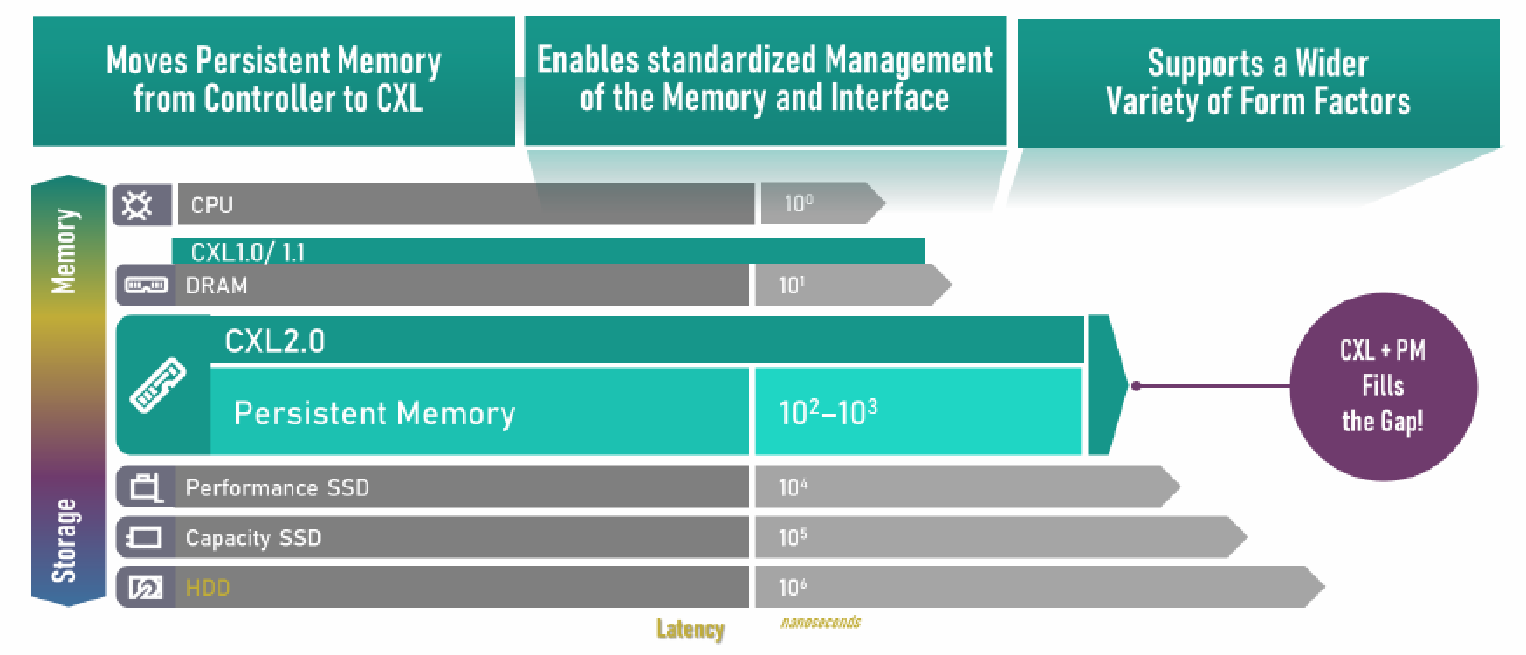

Одно из важных нововведений в индустрии связано с энергонезависимой памятью, которая приближается к DRAM, например, по характеристикам задержки и пропускной способности, обладая преимуществом высокой емкости и постоянной памяти. Это позволяет использовать множество высокопроизводительных приложений, в которых весь набор данных может храниться в памяти.

Одной из проблем архитектуры межсоединений «загрузка-хранилище», такой как CXL, является обеспечение устойчивости (фиксация хранилища данных в постоянной памяти). CXL 2.0 решает эту задачу за счет продуманного алгоритма и стандартного интерфейса управления памятью для программного обеспечения, что позволяет переместить постоянную память с подхода на основе контроллера к прямому управлению памятью (рис. 4).

Рис. 4. CXL 2.0 решает проблему хранения в постоянной памяти

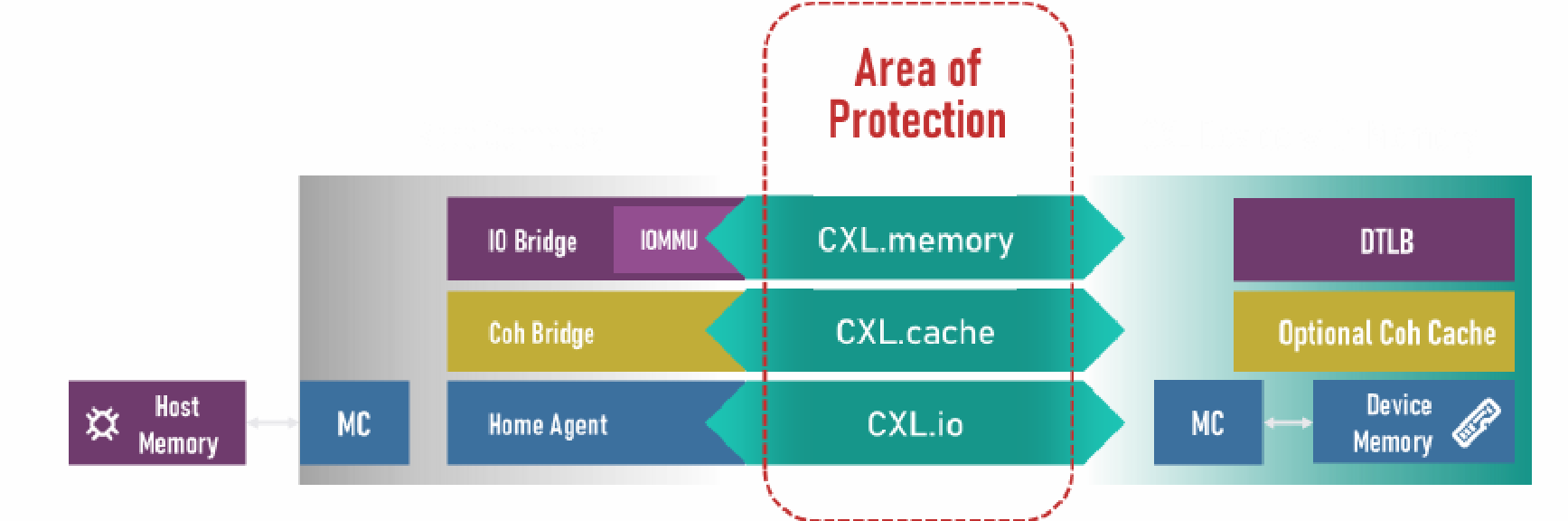

Безопасность является краеугольным камнем успеха любой технологии, учитывая столь распространенные атаки на уязвимости. CXL делает большие успехи в этом отношении, работая совместно с другими отраслевые организации, такие как PCI-SIG и DMTF, чтобы гарантировать беспроблемный пользовательский интерфейс, обеспечивая при этом лучшие механизмы безопасности. CXL 2.0 обеспечивает шифрование канала, которое без проблем работает с существующими механизмами безопасности, такими как устройства TLB, как показано на рис. 5.

Рис. 5. Улучшения безопасности с CXL 2.0

Опубликовав две версии спецификаций за полтора года, Консорциум CXL выходит за рамки CXL 2.0. Основываясь на отзывах компьютерной индустрии и сообщества конечных пользователей, организация работает над следующей версией CXL 3.0, чтобы охватить более полезные сценарии и обеспечить еще более высокую производительность.