Что к чему в «32 нанометрах»

22 декабрь, 2009 - 17:07Тимур ЯгофаровПризнаюсь, при том, что удается довольно много удается бывать на крупных ИТ-конференциях не часто доводится общаться с людьми, имеющими непосредственное отношение к разработке сложных технологий. И вот совсем недавно довелось послушать человека, имеющего непосредственное отношение к разработке той самой 32-нанометровой технологии, по которой уже начат выпуск новых процессоров Intel.

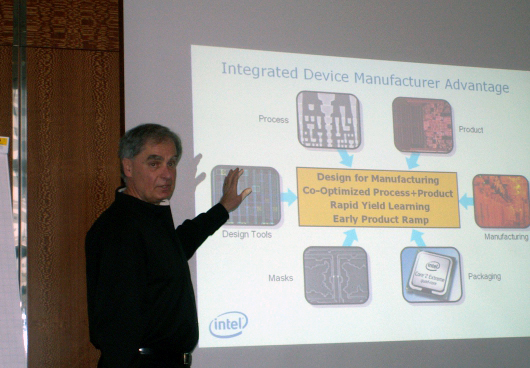

Состоялась эта встреча на так называемом Intel Architecture Workshop, состоявшемся 15 декабря в Мюнхене. Единственным выступлением здесь, на которое не было наложено ограничений по публичному использованию данных из презентации, был доклад Роба Виллонера (Rob Willoner), эксперта из группы технологий производства.

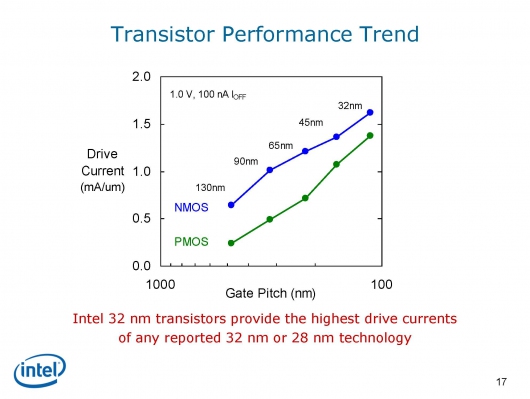

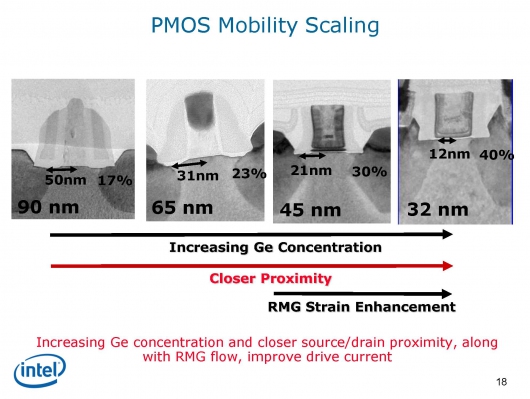

Сначала несколько формальных фактов. Прежде всего, напомню, что нынешний техпроцесс уже относится к четвертому поколению с использованием напряженного кремния. «Напрягать» его нужно для того, чтобы улучшить подвижность частиц, вовлеченных в перенос зарядов. Ведь именно быстродействие транзисторов и является тем самым базисным показателем, который определяет скоростные качества ИС в целом. Так вот в паре транзисторов, включающей вентили типов p-n-p и n-p-n, более медленным всегда является тот, в котором проводимость определяется движением дырок.

Проще всего объяснить этот факт, не вдаваясь глубоко в физику твердого тела, можно на таком примере. Если сравнить активную зону полевого транзистора с рядом кресел на стадионе, а носителям отрицательного заряда (электронам) поставить в соответствие зрителей, то аналогом положительных зарядов (дырок) будут пустые места. И тогда становится ясно, что движение зрителя с одного края пустого ряда к другому будет происходить гораздо быстрее, чем одного пустого места на заполненном зрителями ряду. В последнем случае требуются гораздо более согласованные действия.

![]()

Так вот для повышения подвижности дырок и служит техника «напряжения» кремния. Честно говоря, слабо представлял себе, как это можно сделать в столь миниатюрном объеме, какой занимает транзистор. Оказывается, для этих целей выполняется следующая операция: пространство над затвором заполняется специальным полимером, который удаляется после нанесения следующих слоев металлизации. В результате под затвором возникает небольшая зона локального напряжения. На приведенном выше рисунке она отмечена синим цветом.

Примечательно, что в Intel идет одновременная разработка техпроцессов для выпуска CPU и SoC (System on Chip), поэтому точно также одновременно можно запускать в производство разные типы микросхем с полным набором элементной базы.

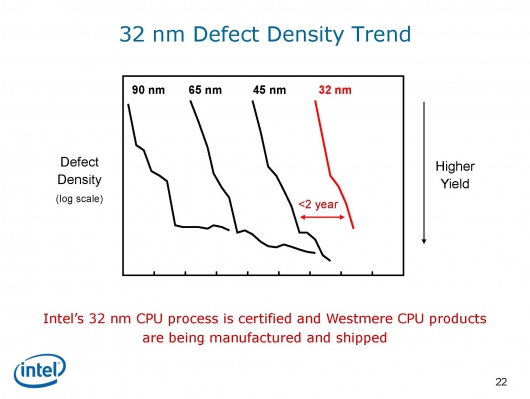

Так вот в новом 32-нанометровом техпроцессе получила свое дальнейшее развитие технология high-k + metal gate (появилось второе ее поколение); на заготовку кремния наносится 9 медных проводящих слоев, перемежающихся low-k диэлектриком; на критически важных слоях чипа была использована иммерсионная литография (это весьма дорогое удовольствие); в процессе выпуска чипов полностью отказались от свинца и инертных газов.

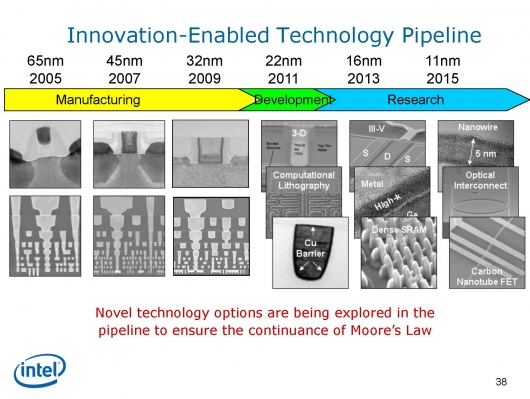

Однако самым важным является то, что данная технология является последней эволюционной, в рамках которой действует закон Мура. Начиная с 22-нанометровой, придется применять принципиально новые подходы к созданию чипов, включая компьютерную литографию и объемное размещение активных элементов. Intel уже выпустила тестовый образец модуля SRAM по технологии 22 нм, но еще требуется основательная проработка процесса.

Как всегда, самое интересное на подобных встречах узнаешь в сессии вопросов и ответов. Среди самых интересных был вопрос о том, зачем вообще заниматься развитием техпроцессов, если и имеющиеся позволяют выпускать достаточно хорошие процессоры. Так вот, оказывается, внедрение нового техпроцесса пока что позволяло Intel с ходу увеличивать прибыль в два раза. Естественно за вычетом расходов на его разработку, что весьма быстро окупалось. Поэтому кроме «высоких целей» по достижению новых рубежей производительности за сменой поколений технологических допусков стоит и чисто «экономическая» подоплека.

Казалось бы, можно было использовать заготовки большего диаметра: вместо нынешних 300 мм взять 400 мм, а то и 450 мм. Но и тут есть серьезные «подводные камни». Во время предыдущего перехода на типоразмер 300 мм разорилось половина поставщиков литографического оборудования и инструментария. Напомню, произошло это в начале 2000 г.г. Поэтому очередной такой переход станет возможен лишь в том случае, если на рынке возникнет резкий рост спроса на микроэлектронику. Да и пока что нет единого мнения о том, каков должен быть следующий стандарт: 400 или 450 мм. Лидеры микроэлектроники в лице Intel, Samsung и TSMC отдают предпочтение 450 мм. Так что удешевление процессоров благодаря использованию пластин большего диаметра пока ждать не приходится…