| +44 –≥–Њ–ї–Њ—Б–∞ |

|

–Я—А–Њ—Ж–µ—Б—Б–Њ—А—Л AMD –њ–Њ–ї—Г—З–∞—В –∞–њ–њ–∞—А–∞—В–љ—Г—О –Ј–∞—Й–Є—В—Г — –≤–Њ –≤–љ—Г—В—А–µ–љ–љ–µ–є –∞—А—Е–Є—В–µ–Ї—В—Г—А–µ CPU –њ–Њ—П–≤–Є—В—Б—П –±–∞—А—М–µ—А –і–ї—П –≤—А–µ–і–Њ–љ–Њ—Б–љ–Њ–≥–Њ –Ї–Њ–і–∞.

–Ъ–∞–Ї –Є–Ј–≤–µ—Б—В–љ–Њ, –Њ–і–љ–Њ–є –Є–Ј –≥–ї–∞–≤–љ—Л—Е –њ—А–Њ–±–ї–µ–Љ –Ј–∞—Й–Є—В—Л –Њ—В —Г—П–Ј–≤–Є–Љ–Њ—Б—В–µ–є Spectre –Є Meltdown —П–≤–ї—П–µ—В—Б—П –Њ–±–µ—Б–њ–µ—З–µ–љ–Є–µ –±–µ–Ј–Њ–њ–∞—Б–љ–Њ—Б—В–Є –њ—А–Є –Љ–Є–љ–Є–Љ–∞–ї—М–љ–Њ–є –њ–Њ—В–µ—А–µ –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В–µ–ї—М–љ–Њ—Б—В–Є. –Ш–љ–∞—З–µ, –њ—А–µ–і–њ—А–Є–љ–Є–Љ–∞–µ–Љ—Л–µ –≤ –±–Њ—А—М–±–µ —Б –≤—А–µ–і–Њ–љ–Њ—Б–љ—Л–Љ –Ї–Њ–і–Њ–Љ –Љ–µ—А—Л –Љ–Њ–≥—Г—В –Њ–Ї–∞–Ј–∞—В—М—Б—П –±–Њ–ї–µ–µ –≤—А–µ–і–Њ–љ–Њ—Б–љ—Л–Љ–Є, —З–µ–Љ —Н—В–Њ—В —Б–∞–Љ—Л–є –Ї–Њ–і. –Ь–Њ–ґ–љ–Њ –Ї–Њ–љ—Б—В–∞—В–Є—А–Њ–≤–∞—В—М, —З—В–Њ –Ї–Њ–Љ–њ–∞–љ–Є—П AMD –њ–Њ–і–Њ—И–ї–∞ –Ї –≤–Њ–њ—А–Њ—Б—Г –і–Њ—Б—В–∞—В–Њ—З–љ–Њ –Њ—Б–љ–Њ–≤–∞—В–µ–ї—М–љ–Њ, –Њ–њ—А–µ–і–µ–ї–Є–≤ —В–∞–Ї—В–Є—З–µ—Б–Ї–Є–µ –Є —Б—В—А–∞—В–µ–≥–Є—З–µ—Б–Ї–Є–µ –љ–∞–њ—А–∞–≤–ї–µ–љ–Є—П.

–Ґ–∞–Ї—В–Є–Ї–∞ –Є —Б—В—А–∞—В–µ–≥–Є—П

–Ф–ї—П –Ї—А–∞—В–Ї–Њ—Б—А–Њ—З–љ–Њ–є –њ–µ—А—Б–њ–µ–Ї—В–Є–≤—Л —А–∞–Ј—А–∞–±–Њ—В–∞–љ–∞ –Є –Њ–њ—В–Є–Љ–Є–Ј–Є—А–Њ–≤–∞–љ–∞ –Љ–µ—В–Њ–і–Є–Ї–∞ –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–є –Љ–Є–љ–Є–Љ–Є–Ј–∞—Ж–Є–Є —А–Є—Б–Ї–Њ–≤, —Б–≤—П–Ј–∞–љ–љ—Л—Е —Б —А–∞–±–Њ—В–Њ–є —А–∞–љ–µ–µ –≤—Л–њ—Г—Й–µ–љ–љ—Л—Е –њ—А–Њ—Ж–µ—Б—Б–Њ—А–Њ–≤. –≠—В–Њ–Љ—Г –њ–Њ—Б–≤—П—Й–µ–љ –і–Њ–Ї—Г–Љ–µ–љ—В Software Techniques Managing Speculation on AMD Processors.

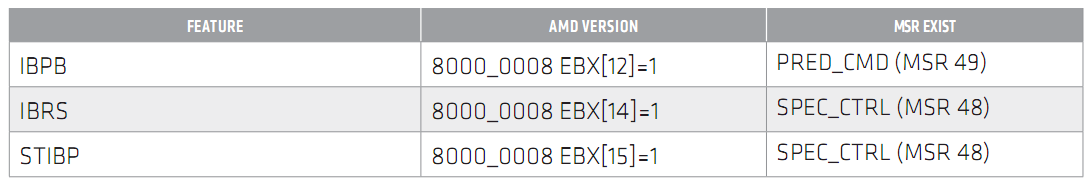

–Я–Њ–ї–љ–Њ–µ —А–µ—И–µ–љ–Є–µ –њ—А–Њ–±–ї–µ–Љ—Л –њ–Њ–і—А–∞–Ј—Г–Љ–µ–≤–∞–µ—В –∞–њ–њ–∞—А–∞—В–љ—Г—О –Љ–Њ–і–µ—А–љ–Є–Ј–∞—Ж–Є—О —З–Є–њ–Њ–≤, –∞ –Є–Љ–µ–љ–љ–Њ — —Д—Г–љ–Ї—Ж–Є–Њ–љ–∞–ї—М–љ—Л–µ —А–∞—Б—И–Є—А–µ–љ–Є—П –∞—А—Е–Є—В–µ–Ї—В—Г—А—Л –њ—А–Њ—Ж–µ—Б—Б–Њ—А–Њ–≤. –Э–∞–±–Њ—А —В–∞–Ї–Є—Е —А–∞—Б—И–Є—А–µ–љ–Є–є –Є —Д–Њ—А–Љ–∞–ї–Є–Ј–∞—Ж–Є—О –Є—Е –і–µ—В–µ–Ї—В–Є—А–Њ–≤–∞–љ–Є—П —З–µ—А–µ–Ј –Є–љ—Б—В—А—Г–Ї—Ж–Є—О CPUID –Њ–њ–Є—Б—Л–≤–∞–µ—В –і–Њ–Ї—Г–Љ–µ–љ—В AMD64 Technology Indirect Branch Control Extension.

–°—Г—В—М –њ—А–µ–і–ї–∞–≥–∞–µ–Љ–Њ–є –Ј–∞—Й–Є—В—Л — –≤ —Б–Њ–Ј–і–∞–љ–Є–Є –∞–њ–њ–∞—А–∞—В–љ–Њ–≥–Њ –±–∞—А—М–µ—А–∞ –љ–∞ –њ—Г—В–Є –≤—Л-–њ–Њ–ї–љ–µ–љ–Є—П –њ—А–Њ–≥—А–∞–Љ–Љ–љ–Њ–≥–Њ –Ї–Њ–і–∞, –Љ–∞–љ–Є–њ—Г–ї–Є—А—Г—О—Й–µ–≥–Њ —В–µ—Е–љ–Є–Ї–∞–Љ–Є –њ–µ—А–µ—Е–Њ–і–Њ–≤ –Є –≤–µ—В–≤–ї–µ–љ–Є–є. –Я—А–µ—Б–ї–µ–і—Г—О—В—Б—П –і–≤–µ —Ж–µ–ї–Є: –і–µ—А–ґ–∞—В—М –≤ —А—Г–Ї–∞—Е –љ–Є—В–Є —Г–њ—А–∞–≤–ї–µ–љ–Є—П –≤—Л—З–Є—Б–ї–Є—В–µ–ї—М–љ—Л–Љ–Є –њ—А–Њ—Ж–µ—Б—Б–∞–Љ–Є –Є –±–ї–Њ–Ї–Є—А–Њ–≤–∞—В—М –Ј–Њ–љ–і–Є—А–Њ–≤–∞–љ–Є–µ «–Ј–∞–њ—А–µ—Й–µ–љ–љ–Њ–є» –њ–∞–Љ—П—В–Є —Б–њ–µ–Ї—Г–ї—П—В–Є–≤–љ—Л–Љ–Є –Њ–њ–µ—А–∞—Ж–Є—П–Љ–Є. –Я–ї–∞–љ–Є—А—Г–µ—В—Б—П, —З—В–Њ –њ—А–Є–љ–Є–Љ–∞–µ–Љ—Л–µ –Љ–µ—А—Л –Њ–±–µ—Б–њ–µ—З–∞—В –љ–∞–і–µ–ґ–љ—Л–є –Ј–∞—Б–ї–Њ–љ –њ—А–Њ—В–Є–≤ —Г—П–Ј–≤–Є–Љ–Њ—Б—В–µ–є Spectre –Є Meltdown.

–Ю —В–µ–Ї—Г—Й–µ–Љ –њ–Њ–ї–Њ–ґ–µ–љ–Є–Є –і–µ–ї

–Ш—Б—Б–ї–µ–і—Г—П —Б–µ–≥–Њ–і–љ—П—И–љ—О—О —Б–њ–Њ—Б–Њ–±–љ–Њ—Б—В—М –њ—А–Њ—Ж–µ—Б—Б–Њ—А–Њ–≤ AMD –њ—А–Њ—В–Є–≤–Њ—Б—В–Њ—П—В—М —Е–∞–Ї–µ—А—Б–Ї–Є–Љ –∞—В–∞–Ї–∞–Љ –Њ—В–Љ–µ—В–Є–Љ, —З—В–Њ –Њ–љ–Є —Е–Њ—В—П –Є –≥–Њ—В–Њ–≤—Л –Ї –Є–љ–Є—Ж–Є–∞—В–Є–≤–∞–Љ —А–∞–Ј—А–∞–±–Њ—В-—З–Є–Ї–Њ–≤, —Б–Њ—Б—В–Њ—П–љ–Є–µ –≤–љ—Г—В—А–µ–љ–љ–µ–є –Ј–∞—Й–Є—В—Л –і–∞–ї–µ–Ї–Њ –Њ—В –ґ–µ–ї–∞–µ–Љ–Њ–≥–Њ. –Я—А–Њ–∞–љ–∞–ї–Є-–Ј–Є—А—Г–µ–Љ –∞—А—Е–Є—В–µ–Ї—В—Г—А—Г AMD Ryzen 5 1600 Six-Core Processor –љ–∞ –≥–µ–є–Љ–µ—А—Б–Ї–Њ–є –њ–ї–∞—В—Д–Њ—А–Љ–µ MSI X370 XPower Gaming Titanium.

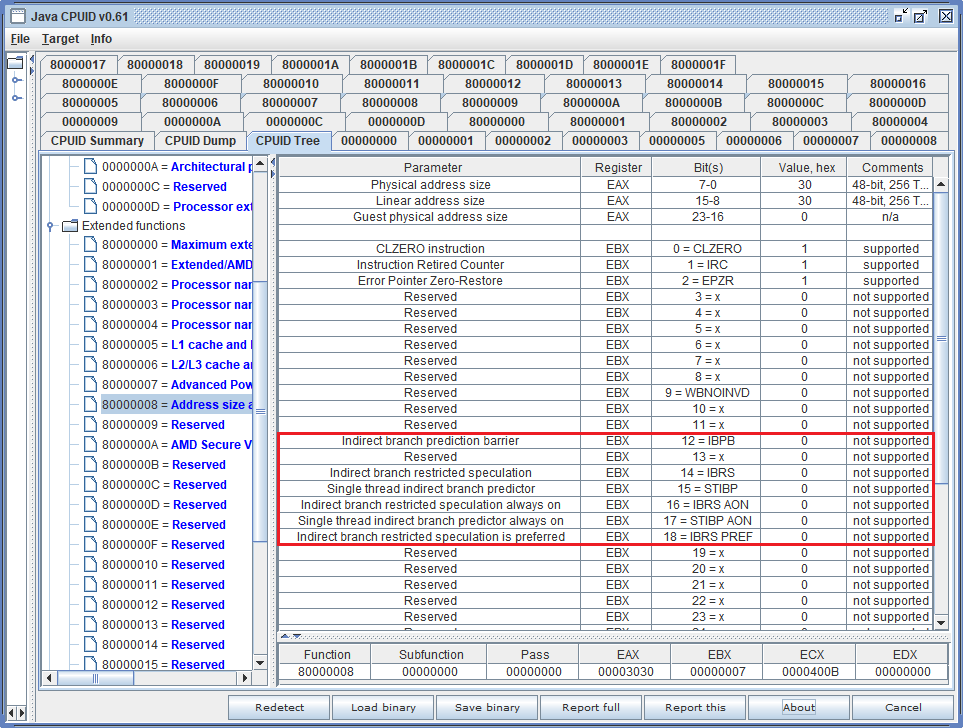

–†–Є—Б 1. –†–µ–Ј—Г–ї—М—В–∞—В —А–∞–±–Њ—В—Л —Г—В–Є–ї–Є—В—Л JavaCrossPlatformCPUID v0.61: —Б–Њ–і–µ—А–ґ–Є-–Љ–Њ–µ —А–µ–≥–Є—Б—В—А–∞ EBX –њ–Њ—Б–ї–µ –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П —Д—Г–љ–Ї—Ж–Є–Є 80000008h

–£—В–Є–ї–Є—В–∞ JavaCrossPlatformCPUID, —А–∞–Ј—А–∞–±–Њ—В–∞–љ–љ–∞—П –≤ IC Book Labs, –і–∞–µ—В –њ—А–µ–і—Б—В–∞–≤–ї–µ–љ–Є–µ –Њ –±–Є—В–Њ–≤—Л—Е –њ–Њ–ї—П—Е –Є –Њ–±—К–µ–Ї—В–∞—Е –≤–љ—Г—В—А–µ–љ–љ–µ–є –∞—А—Е–Є—В–µ–Ї—В—Г—А—Л –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞, –Њ—В–≤–µ—В—Б—В–≤–µ–љ–љ—Л—Е –Ј–∞ –≤–љ–µ–і—А–µ–љ–Є–µ –Ј–∞—Й–Є—В—Л –њ—А–Њ—В–Є–≤ –Ј–ї–Њ–≤—А–µ–і–љ–Њ–≥–Њ –Ї–Њ–і–∞.

–Ъ–∞–Ї –≤–Є–і–Є–Љ, —А–µ–≥–Є—Б—В—А EBX –њ–Њ—Б–ї–µ –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П —Д—Г–љ–Ї—Ж–Є–Є CPUID 80000008h –і–Њ–ї–ґ–µ–љ —Б–Њ–і–µ—А–ґ–∞—В—М –±–Є—В–Њ–≤—Л–µ —Д–ї–∞–≥–Є, —Б–≤–Є–і–µ—В–µ–ї—М—Б—В–≤—Г—О—Й–Є–µ –Њ –љ–∞–ї–Є—З–Є–Є —А–∞—Б—И–Є—А–µ-–љ–Є–є «Indirect Branch Control Extension», –Ј–∞—П–≤–ї–µ–љ–љ—Л—Е –≤ –Њ–Ј–љ–∞—З–µ–љ–љ–Њ–Љ –≤—Л—И–µ –Ї–Њ—А–њ–Њ—А–∞—В–Є–≤–љ–Њ–Љ –і–Њ–Ї—Г–Љ–µ–љ—В–µ.

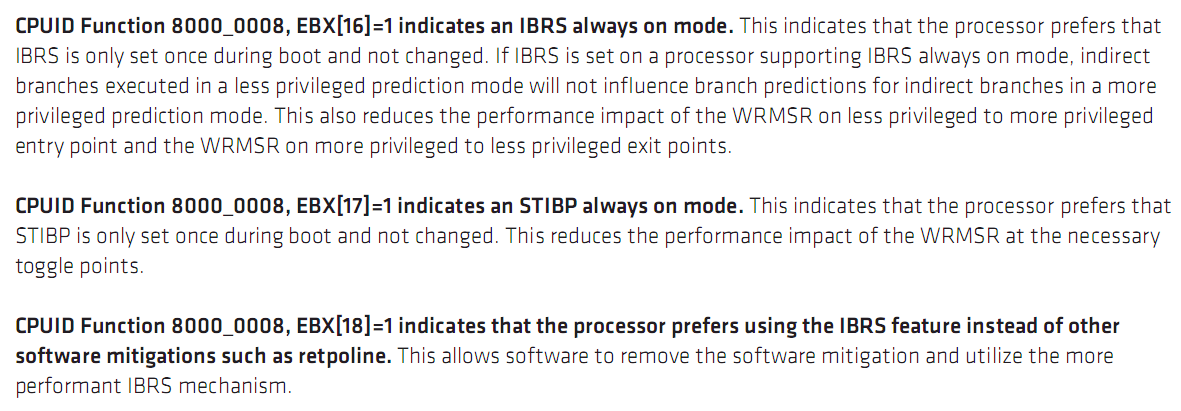

–†–Є—Б 2. –†–µ–≥–Є—Б—В—А EBX –њ–Њ—Б–ї–µ –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П —Д—Г–љ–Ї—Ж–Є–Є CPUID 80000008h —Б–Њ–і–µ—А–ґ–Є—В –±–Є—В–Њ–≤—Л–µ —Д–ї–∞–≥–Є, –Є–љ–і–Є—Ж–Є—А—Г—О—Й–Є–µ –љ–∞–ї–Є—З–Є–µ —Д—Г–љ–Ї—Ж–Є–Њ–љ–∞–ї—М–љ—Л—Е —А–∞—Б—И–Є—А–µ–љ–Є–є

–Ш—Е —Д—Г–љ–Ї—Ж–Є–Њ–љ–∞–ї—М–љ–Њ—Б—В—М –Љ–Њ–ґ–љ–Њ —А–∞–Ј–і–µ–ї–Є—В—М –љ–∞ —В—А–Є —Б–Њ—Б—В–∞–≤–ї—П—О—Й–Є–µ, –Ї–∞–ґ–і–∞—П –Є–Ј –Ї–Њ—В–Њ—А—Л—Е –і–µ–Ї–ї–∞—А–Є—А—Г–µ—В—Б—П —А–∞–Ј–і–µ–ї—М–љ–Њ:

-

Indirect Branch Prediction Barrier (IBPB)

-

Indirect Branch Restricted Speculation (IBRS)

-

Single Thread Indirect Branch Predictor (STIBP)

–Ф–Њ–њ–Њ–ї–љ–Є—В–µ–ї—М–љ—Л–µ –њ–Њ–ї—П –љ–µ—Б—Г—В –Є–љ—Д–Њ—А–Љ–∞—Ж–Є—О –Њ–± –Њ–њ—В–Є–Љ–∞–ї—М–љ—Л—Е —Б—Ж–µ–љ–∞—А–Є—П—Е –Є—Б-–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є—П –Ј–∞—Й–Є—В—Л, –Њ–±–µ—Б–њ–µ—З–Є–≤–∞—О—Й–Є—Е –Љ–Є–љ–Є–Љ–Є–Ј–∞—Ж–Є—О –µ–µ –≤–ї–Є—П–љ–Є—П –љ–∞ –њ—А–Њ–Є–Ј-–≤–Њ–і–Є—В–µ–ї—М–љ–Њ—Б—В—М –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞.

–†–Є—Б 3. –†–µ–≥–Є—Б—В—А EBX –њ–Њ—Б–ї–µ –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П —Д—Г–љ–Ї—Ж–Є–Є CPUID 80000008h —Б–Њ–і–µ—А–ґ–Є—В –±–Є—В–Њ–≤—Л–µ —Д–ї–∞–≥–Є, –Њ–њ—А–µ–і–µ–ї—П—О—Й–Є–µ –Њ–њ—В–Є–Љ–∞–ї—М–љ—Л–µ —Б—Ж–µ–љ–∞—А–Є–Є –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є—П —Д—Г–љ–Ї—Ж–Є–Њ–љ–∞–ї—М–љ—Л—Е —А–∞—Б—И–Є—А–µ–љ–Є–є

–Х–і–Є–љ–Є—З–љ–Њ–µ –Ј–љ–∞—З–µ–љ–Є–µ —Д–ї–∞–≥–∞ «IBRS always on mode» –Њ–Ј–љ–∞—З–∞–µ—В, —З—В–Њ –Њ–њ—В–Є–Љ–∞–ї—М–љ–∞—П –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В–µ–ї—М–љ–Њ—Б—В—М –і–Њ—Б—В–Є–≥–∞–µ—В—Б—П –≤ —В–Њ–Љ —Б–ї—Г—З–∞–µ, –µ—Б–ї–Є —А–µ–ґ–Є–Љ IBRS –±—Г–і–µ—В –≤–Ї–ї—О—З–µ–љ UEFI BIOS –њ—А–Є —Б—В–∞—А—В–µ –њ–ї–∞—В—Д–Њ—А–Љ—Л –Є –∞–Ї—В–Є–≤–µ–љ –њ–Њ—Б—В–Њ—П–љ–љ–Њ, —В–∞–Ї –Ї–∞–Ї –≤–ї–Є—П–љ–Є–µ IBRS –љ–∞ –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В–µ–ї—М–љ–Њ—Б—В—М –Љ–Є–љ–Є–Љ–∞–ї—М–љ–Њ. –Ш–љ–∞—З–µ, –њ—А–µ–і–њ–Њ—З—В–Є—В–µ–ї—М–љ–µ–µ –і–Є–љ–∞–Љ–Є—З–µ—Б–Ї–Њ–µ –њ–µ—А–µ–Ї–ї—О—З–µ–љ–Є–µ IBRS –≤ —Б–Њ–Њ—В–≤–µ—В—Б—В–≤–Є–Є —Б –њ—А–Є–≤–Є–ї–µ–≥–Є—П–Љ–Є –≤—Л–њ–Њ–ї–љ—П–µ–Љ–Њ–≥–Њ –Ї–Њ–і–∞. –§–∞–Ї—В–Є—З–µ—Б–Ї–Є, —Н—В–Њ –Њ—В–≤–µ—В –љ–∞ –≤–Њ–њ—А–Њ—Б, —З—В–Њ –њ—А–Є–≤–Њ–і–Є—В –Ї –Љ–µ–љ—М—И–Є–Љ –њ–Њ—В–µ—А—П–Љ –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В–µ–ї—М–љ–Њ—Б—В–Є: –њ–Њ—Б—В–Њ—П–љ–љ–∞—П –∞–Ї—В–Є–≤–љ–Њ—Б—В—М IBRS –Є–ї–Є –Њ–њ–µ—А–∞—Ж–Є–Є –њ–µ—А–µ–Ї–ї—О—З–µ–љ–Є—П —А–µ–ґ–Є–Љ–∞ IBRS.

–§–ї–∞–≥ «STIBP always on mode» –Ј–∞–і–∞–µ—В –∞–љ–∞–ї–Њ–≥–Є—З–љ—Г—О –Њ–њ—Ж–Є—О –і–ї—П —А–µ–ґ–Є–Љ–∞ STIBP.

–§–ї–∞–≥ «Processor prefers using the IBRS feature» –Њ–Ј–љ–∞—З–∞–µ—В, —З—В–Њ —Б–љ–Є–ґ–µ–љ–Є–µ –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В–µ–ї—М–љ–Њ—Б—В–Є, –Њ–±—Г—Б–ї–Њ–≤–ї–µ–љ–љ–Њ–µ –≤–Ї–ї—О—З–µ–љ–Є–µ–Љ IBRS, –Љ–µ–љ—М—И–µ, —З–µ–Љ –њ—А–Є –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є–Є –њ—А–Њ–≥—А–∞–Љ–Љ–љ—Л—Е —В–µ—Е–љ–Є–Ї, —В–∞–Ї–Є—Е –Ї–∞–Ї retpoline, –њ–Њ—Н—В–Њ–Љ—Г –Ј–∞–і–µ–є—Б—В-–≤–Њ–≤–∞—В—М IBRS –њ—А–µ–і–њ–Њ—З—В–Є—В–µ–ї—М–љ–µ–µ –љ–µ —В–Њ–ї—М–Ї–Њ —Б —В–Њ—З–Ї–Є –Ј—А–µ–љ–Є—П –±–µ–Ј–Њ–њ–∞—Б–љ–Њ—Б—В–Є, –љ–Њ –Є –њ—А–Њ–Є–Ј–≤–Њ–і–Є—В–µ–ї—М–љ–Њ—Б—В–Є.

–Ґ–∞–Ї–Є–Љ –Њ–±—А–∞–Ј–Њ–Љ, –њ–Њ—Б–ї–µ –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П –Є–љ—Б—В—А—Г–Ї—Ж–Є–Є CPUID, —Б–Є—Б—В–µ–Љ–љ–Њ–Љ—Г –њ—А–Њ–≥—А–∞–Љ-–Љ–Є—Б—В—Г –і–Њ—Б—В—Г–њ–љ–∞ –Є–љ—Д–Њ—А–Љ–∞—Ж–Є—П –љ–µ —В–Њ–ї—М–Ї–Њ –Њ –љ–Њ–≤—Л—Е –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В—П—Е –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞, –љ–Њ –Є –Њ–њ—В–Є–Љ–∞–ї—М–љ—Л—Е —Б—Ж–µ–љ–∞—А–Є—П—Е –Є—Е –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞–љ–Є—П.

–†–∞—Б—Б–Љ–Њ—В—А–Є–Љ —В—А–Є —Б–Њ—Б—В–∞–≤–ї—П—О—Й–Є–µ –∞–њ–њ–∞—А–∞—В–љ–Њ–є –Ј–∞—Й–Є—В—Л.

Indirect Branch Prediction Barrier

–Ю—Б–љ–Њ–≤–љ—Л–Љ –Њ–±—К–µ–Ї—В–Њ–Љ –∞—В–∞–Ї —Б–Њ —Б—В–Њ—А–Њ–љ—Л –≤—А–µ–і–Њ–љ–Њ—Б–љ–Њ–≥–Њ –Ї–Њ–і–∞ —Б—В–∞–ї Branch Predictor –Є–ї–Є –±–ї–Њ–Ї –њ—А–µ–і—Б–Ї–∞–Ј–∞–љ–Є—П –≤–µ—В–≤–ї–µ–љ–Є–є, –Њ–њ—В–Є–Љ–Є–Ј–Є—А—Г—О—Й–Є–є –≤—Л–њ–Њ–ї–љ–µ–љ–Є–µ –Ї–Њ–Љ–∞–љ–і –Ї–Њ—Б–≤–µ–љ–љ—Л—Е –њ–µ—А–µ—Е–Њ–і–Њ–≤ –љ–∞ –Њ—Б–љ–Њ–≤–∞–љ–Є–Є —А–∞–љ–µ–µ —Б–Њ–±—А–∞–љ–љ–Њ–є —Б—В–∞—В–Є—Б—В–Є–Ї–Є. –°–њ–Њ—Б–Њ–±–љ–Њ—Б—В—М –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞ –Ј–∞–њ–Њ–Љ–Є–љ–∞—В—М –њ—А–µ–і—Л—Б—В–Њ—А–Є—О –≤–µ—В–≤–ї–µ–љ–Є–є, –і–∞–µ—В –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В—М –∞—В–∞–Ї—Г—О—Й–µ–є –Ј–∞–і–∞—З–µ, –≤—Л–њ–Њ–ї–љ–Є–≤ —Д—А–∞–≥–Љ–µ–љ—В –Ї–Њ–і–∞ —Б —В—А–µ–±—Г–µ–Љ–Њ–є –њ–Њ-—Б–ї–µ–і–Њ–≤–∞—В–µ–ї—М–љ–Њ—Б—В—М—О –Ї–Њ—Б–≤–µ–љ–љ—Л—Е –њ–µ—А–µ—Е–Њ–і–Њ–≤, –≤–ї–Є—П—В—М –љ–∞ —Е–Њ–і —Б–њ–µ–Ї—Г–ї—П—В–Є–≤–љ–Њ–≥–Њ –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П –≤ –∞—В–∞–Ї—Г–µ–Љ–Њ–є –Ј–∞–і–∞—З–µ –Є –і–Њ–±—Л–≤–∞—В—М –Є–љ—Д–Њ—А–Љ–∞—Ж–Є—О –Њ –њ–Њ—Б–ї–µ–і–љ–µ–є, –њ–Њ–ї—М–Ј—Г—П—Б—М –њ–Њ–±–Њ—З–љ—Л–Љ–Є —Н—Д—Д–µ–Ї—В–∞–Љ–Є, –љ–∞–њ—А–Є–Љ–µ—А, — –Є–Ј–Љ–µ–љ–µ–љ–Є–µ–Љ —В–∞–є–Љ–Є–љ–≥–Њ–≤.

–Ы–Њ–≥–Є—З–љ–Њ–є —А–µ–∞–Ї—Ж–Є–µ–є —А–∞–Ј—А–∞–±–Њ—В—З–Є–Ї–Њ–≤ –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞ —Б—В–∞–ї–∞ —А–µ–∞–ї–Є–Ј–∞—Ж–Є—П —Б–≤–Њ–µ–Њ–±—А–∞–Ј–љ–Њ–≥–Њ –±–∞—А—М–µ—А–∞, —А–∞–Ј–і–µ–ї—П—О—Й–µ–≥–Њ –і–≤–∞ —Г—З–∞—Б—В–Ї–∞ –≤—Л–њ–Њ–ї–љ—П–µ–Љ–Њ–≥–Њ –Ї–Њ–і–∞. –Я—А–Є —Н—В–Њ–Љ –≥–∞—А–∞–љ—В–Є—А—Г–µ—В—Б—П, —З—В–Њ —Б—В–∞—В–Є—Б—В–Є–Ї–∞ –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П, –љ–∞–Ї–Њ–њ–ї–µ–љ–љ–∞—П –і–Њ –±–∞—А—М–µ—А–∞, –±—Г–і–µ—В –Њ—З–Є—Й–µ–љ–∞ –Є –љ–µ –њ–Њ–≤–ї–Є—П–µ—В –љ–∞ —Б–њ–µ–Ї—Г–ї—П—В–Є–≤–љ—Г—О –Њ–±—А–∞–±–Њ—В–Ї—Г –Є–љ—Б—В—А—Г–Ї—Ж–Є–є JMP, CALL, RET –≤—Л–њ–Њ–ї–љ—П–µ–Љ—Л—Е –њ–Њ—Б–ї–µ –±–∞—А—М–µ—А–∞.

–Т —З–∞—Б—В–љ–Њ—Б—В–Є, —Н—В–Њ –њ–Њ–Ј–≤–Њ–ї—П–µ—В –Њ—Б—Г—Й–µ—Б—В–≤–Є—В—М –Є–Ј–Њ–ї—П—Ж–Є—О –≥–Њ—Б—В–µ–≤—Л—Е –Ј–∞–і–∞—З –≤–Є—А—В—Г-–∞–ї—М–љ–Њ–є –Љ–∞—И–Є–љ—Л, –∞ —В–∞–Ї–ґ–µ –Є—Б–Ї–ї—О—З–Є—В—М –Є—Е –≤–ї–Є—П–љ–Є–µ –љ–∞ –≥–Є–њ–µ—А–≤–Є–Ј–Њ—А –≤–Є—А—В—Г–∞–ї–Є–Ј–∞—Ж–Є–Є. –Ф–ї—П –Њ–±–Њ–Ј–љ–∞—З–µ–љ–Є—П —В–Њ—З–Ї–Є –±–∞—А—М–µ—А–∞ –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –Њ–њ–µ—А–∞—Ж–Є—П –Ј–∞–њ–Є—Б–Є –≤ –Њ–і–Є–љ –Є–Ј Model-Specific —А–µ–≥–Є—Б—В—А–Њ–≤ –њ—А–Њ—Ж–µ—Б—Б–Њ—А–∞ (PRED_CMD).

Indirect Branch Restricted Speculation

–§—Г–љ–Ї—Ж–Є–Њ–љ–∞–ї—М–љ–Њ—Б—В—М IBRS, —В–∞–Ї –ґ–µ –Ї–∞–Ї IBPB, –Њ–≥—А–∞–љ–Є—З–Є–≤–∞–µ—В –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В—М –Ј–ї–Њ—Г–њ–Њ—В—А–µ–±–ї–µ–љ–Є–є, –Њ—Б–љ–Њ–≤–∞–љ–љ—Л—Е –љ–∞ —Б–њ–µ–Ї—Г–ї—П—В–Є–≤–љ–Њ–Љ –≤—Л–њ–Њ–ї–љ–µ–љ–Є–Є –Є–љ—Б—В—А—Г–Ї—Ж–Є–є –Ї–Њ—Б–≤–µ–љ–љ–Њ–є –њ–µ—А–µ–і–∞—З–Є —Г–њ—А–∞–≤–ї–µ–љ–Є—П. IBRS –±–∞–Ј–Є—А—Г–µ—В—Б—П –љ–∞ –Ї–ї–∞—Б—Б–Є—З–µ—Б–Ї–Є—Е —Г—А–Њ–≤–љ—П—Е –њ—А–Є–≤–Є–ї–µ–≥–Є–є Protected Mode –Є –љ–∞ –Њ—В–љ–Њ—И–µ–љ–Є—П—Е «–≥–Є–њ–µ—А–≤–Є–Ј–Њ—А-–≥–Њ—Б—В—М» –≤ —Б–Є—Б—В–µ–Љ–∞—Е —Б –≤–Є—А—В—Г–∞–ї–Є–Ј–∞—Ж–Є–µ–є. –Ґ–Є–њ–Њ–≤–Њ–є —Б—Ж–µ–љ–∞—А–Є–є –њ—А–Є–Љ–µ–љ–µ–љ–Є—П IBRS –њ–Њ–Ј–≤–Њ–ї—П–µ—В –Є—Б–Ї–ї—О—З–Є—В—М –≤–ї–Є—П–љ–Є–µ –њ—А–Њ—Ж–µ—Б—Б–Њ–≤ —Г—А–Њ–≤–љ—П –њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї—П (ring 3) –љ–∞ –њ—А–Є–≤–Є–ї–µ–≥–Є-—А–Њ–≤–∞–љ–љ—Л–µ –њ—А–Њ—Ж–µ–і—Г—А—Л –Њ–њ–µ—А–∞—Ж–Є–Њ–љ–љ–Њ–є —Б–Є—Б—В–µ–Љ—Л (ring 0), –∞ —В–∞–Ї–ґ–µ –≤–ї–Є—П–љ–Є–µ –≥–Њ—Б-—В–µ–≤–Њ–є –Ј–∞–і–∞—З–Є –љ–∞ –≥–Є–њ–µ—А–≤–Є–Ј–Њ—А –≤–Є—А—В—Г–∞–ї–Є–Ј–∞—Ж–Є–Є.

–Ф–ї—П –≤–Ї–ї—О—З–µ–љ–Є—П IBRS –Є—Б–њ–Њ–ї—М–Ј—Г–µ—В—Б—П –Њ–і–Є–љ –Є–Ј Model-Specific —А–µ–≥–Є—Б—В—А–Њ–≤ –њ—А–Њ—Ж–µ—Б-—Б–Њ—А–∞ (SPEC_CTRL, bit 0). –Т —А–µ–ґ–Є–Љ–µ IBRS, —Б—В–∞—В–Є—Б—В–Є–Ї–∞, –љ–∞–Ї–Њ–њ–ї–µ–љ–љ–∞—П –њ—А–Є –≤—Л-–њ–Њ–ї–љ–µ–љ–Є–Є –Љ–µ–љ–µ–µ –њ—А–Є–≤–Є–ї–µ–≥–Є—А–Њ–≤–∞–љ–љ–Њ–≥–Њ –Ї–Њ–і–∞, –љ–µ –±—Г–і–µ—В –Њ–Ї–∞–Ј—Л–≤–∞—В—М –≤–ї–Є—П–љ–Є–µ –љ–∞ —Е–Њ–і —Б–њ–µ–Ї—Г–ї—П—В–Є–≤–љ–Њ–≥–Њ –≤—Л–њ–Њ–ї–љ–µ–љ–Є—П –і—А—Г–≥–Є—Е –Ј–∞–і–∞—З.

Single Thread Indirect Branch Predictor

–Ю–њ—Ж–Є—П STIBP, —Г–њ—А–∞–≤–ї—П–µ–Љ–∞—П –Њ–і–љ–Є–Љ –Є–Ј Model-Specific —А–µ–≥–Є—Б—В—А–Њ–≤ (SPEC_CTRL, bit 1), —В–∞–Ї–ґ–µ –Ї–∞–Ї –Є –і–≤–µ —А–∞–љ–µ–µ —А–∞—Б—Б–Љ–Њ—В—А–µ–љ–љ—Л–µ, –Њ–≥—А–∞–љ–Є—З–Є–≤–∞–µ—В –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В–Є –Ј–ї–Њ–љ–∞–Љ–µ—А–µ–љ–љ–Њ–≥–Њ –њ—А–Є–Љ–µ–љ–µ–љ–Є—П –њ—А–µ–і–Є–Ї—В–Њ—А–∞. –§—Г–љ–Ї—Ж–Є–Њ–љ–∞–ї—М–љ–Њ—Б—В—М STIBP –њ—А–µ–і–љ–∞–Ј-–љ–∞—З–µ–љ–∞ –і–ї—П —А–µ—И–µ–љ–Є—П –њ—А–Њ–±–ї–µ–Љ—Л, –Є–Љ–µ—О—Й–µ–є –Љ–µ—Б—В–Њ –≤ —Б–ї—Г—З–∞–µ, –Ї–Њ–≥–і–∞ –љ–µ—Б–Ї–Њ–ї—М–Ї–Њ –ї–Њ–≥–Є—З–µ—Б–Ї–Є—Е –њ—А–Њ—Ж–µ—Б—Б–Њ—А–Њ–≤ (–Ї–∞–Ї –њ—А–∞–≤–Є–ї–Њ, –і–≤–∞) —Б–Њ–≤–Љ–µ—Б—В–љ–Њ –Є—Б–њ–Њ–ї—М–Ј—Г—О—В –Њ–±—Й–Є–є –±–ї–Њ–Ї –њ—А–µ–і—Б–Ї–∞–Ј–∞–љ–Є—П –≤–µ—В–≤–ї–µ–љ–Є–є, —З—В–Њ –і–∞–µ—В –≤–Њ–Ј–Љ–Њ–ґ–љ–Њ—Б—В—М –∞—В–∞–Ї—Г—О—Й–µ–Љ—Г –њ–Њ—В–Њ–Ї—Г –≤–Њ–Ј–і–µ–є—Б—В–≤–Њ–≤–∞—В—М –љ–∞ –∞—В–∞–Ї—Г–µ–Љ—Л–є –њ–Њ—В–Њ–Ї, –≤—Л–њ–Њ–ї–љ—П–µ–Љ—Л–є –љ–∞ —Б–Њ—Б–µ–і–љ–µ–Љ –ї–Њ–≥–Є—З–µ—Б–Ї–Њ–Љ –њ—А–Њ—Ж–µ—Б—Б–Њ—А–µ.

–Р–љ–∞–ї–Є–Ј–Є—А—Г—П –њ–µ—А—Б–њ–µ–Ї—В–Є–≤—Г

–Э–µ—Б–Љ–Њ—В—А—П –љ–∞ —В–Њ, —З—В–Њ –≤ —Б–µ–≥–Њ–і–љ—П—И–љ–µ–є –∞—А—Е–Є—В–µ–Ї—В—Г—А–µ AMD –Ј–∞—Й–Є—В–љ—Л–є –±–∞—А—М–µ—А –љ–∞ –њ—Г—В–Є –≤—А–µ–і–Њ–љ–Њ—Б–љ–Њ–≥–Њ –Ї–Њ–і–∞, —Н–Ї—Б–њ–ї—Г–∞—В–Є—А—Г—О—Й–µ–≥–Њ –Є–Ј–≤–µ—Б—В–љ—Л–µ —Г—П–Ј–≤–Є–Љ–Њ—Б—В–Є CPU, —Д–∞–Ї—В–Є—З–µ—Б–Ї–Є –Њ—В—Б—Г—В—Б—В–≤—Г–µ—В, –≥–Њ—В–Њ–≤–љ–Њ—Б—В—М –љ–µ–Ј–∞–Љ–µ–і–ї–Є—В–µ–ї—М–љ–Њ –њ—А–Є–љ—П—В—М –Љ–µ—А—Л –њ—А–Њ—В–Є–≤ –љ–µ—Б–∞–љ–Ї—Ж–Є–Њ–љ–Є—А–Њ–≤–∞–љ–љ–Њ–≥–Њ –і–Њ—Б—В—Г–њ–∞ –Ї –Ї–Њ–Љ–њ—М—О—В–µ—А–љ—Л–Љ —А–µ—Б—Г—А—Б–∞–Љ –Љ–Њ–ґ–љ–Њ —В–Њ–ї—М–Ї–Њ –њ—А–Є–≤–µ—В—Б—В–≤–Њ–≤–∞—В—М. –° —В–µ—Е –њ–Њ—А, –Ї–∞–Ї –њ—А–Њ—Ж–µ—Б—Б–Њ—А—Л –љ–∞—З–∞–ї–Є –Є—Б–њ–Њ–ї—М–Ј–Њ–≤–∞—В—М –Њ–±–љ–Њ–≤–ї–µ–љ–Є–µ –Љ–Є–Ї—А–Њ–Ї–Њ–і–∞, –∞–њ–≥—А–µ–є–і –Є—Е –∞–њ–њ–∞—А–∞—В–љ–Њ–є –Ј–∞—Й–Є—В—Л –Љ–Њ–ґ–µ—В –њ—А–Њ–Є–Ј–Њ–є—В–Є –љ–µ —В–Њ–ї—М–Ї–Њ –≤ —А–µ–Ј—Г–ї—М—В–∞—В–µ —Д–Є–Ј–Є—З–µ—Б–Ї–Њ–є –Ј–∞–Љ–µ–љ—Л —З–Є–њ–∞, –љ–Њ –Є –Њ–Ї–∞–Ј–∞—В—М—Б—П –њ—А–Є—П—В–љ—Л–Љ —Б—О—А–њ—А–Є–Ј–Њ–Љ –і–ї—П –њ–Њ–ї—М–Ј–Њ–≤–∞—В–µ–ї—П — –њ–Њ—Б–ї–µ «–њ–µ—А–µ—И–Є–≤–Ї–Є» UEFI BIOS, —А–∞–Ј—Г–Љ–µ–µ—В—Б—П.

–°—В—А–∞—В–µ–≥—Ц—П –Њ—Е–Њ–ї–Њ–і–ґ–µ–љ–љ—П –¶–Ю–Ф –і–ї—П –µ–њ–Њ—Е–Є AI

| +44 –≥–Њ–ї–Њ—Б–∞ |

|