Разработана самая миниатюрная ячейка для следующих поколений SRAM

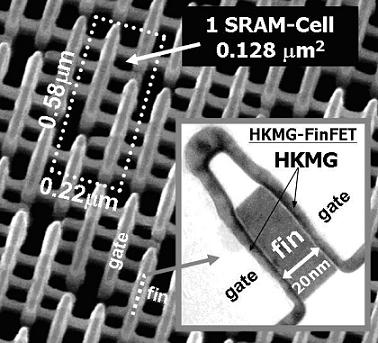

Итогом сотрудничества Toshiba, IBM и AMD стала анонсированная ими на 2008 International Electron Devices Meeting (IEDM) самая миниатюрная фунционирующая ячейка памяти SRAM. Устройство площадью 0,128 мкм2 разработано с применением технологий high-k/metal gate (HKMG) на базе транзисторов FinFET и предлагает ряд преимуществ по сравнению с планарными FET-ячейками.

Чтобы уменьшить размеры планарных транзисторов в SRAM чипмейкерам приходится вводить больше дефектов в зону устройства, что приводит к нежелательному разбросу характеристик и ухудшает стабильность работы. Особенно критичной эта проблема становится при достижении уроня детализации 22 нм. Применение FinFET - вертикальных транзисторов с нелегированными кремниевыми каналами пластинчатой формы (Fin), это альтернативный способ миниатюризации ячеек SRAM с меньшей вариативностью характеристик.

Образцы ячеек FinFET, полученные инженерами трех компаний-партнеров, уступают по площади самым миниатюрным непланарным ячейкам, изготовлявшимся ранее, более чем вполовину. Для достижения такого результата иследовательскому коллективу потребовалось оптимизировать производственные процессы нанесения и удаления материала (в том числе HKMG) для вертикальных поверхностей непланарной структуры FinFET. Ученые экспериментально установили, что использование FET с нелегированными каналами увеличивает стабильность характеристик более, чем на 28%.